前面講的都是功能仿真 ,都是理想的仿真,驗證代碼的功能。

前仿只是完成了一部分。

- 器件自身的延遲

- 連線的延遲

取決於器件的類型,工藝有關。后仿真更加關注toggle的覆蓋率

后仿真是十分慢的,門級仿真特別花

1. 課程目標

DC綜合之后,得到的網表會將觸發器,連線器件的延遲,反標到網表中,都是算法得到的。

怎么樣時序信息提取出來后反標

2. 門級驗證的流程

PPT1

DC是不含物理信息的

PPT2

PPT3

綜合是否保持層次化,視情況而定

3. 門級驗證的時序信息

- race命令,把沖突結果放到日志里面

4. 時序信息反標到門級網表

PPT1

把SDF文件反標的仿真文件中,用到了仿真的庫

第二種方式

PPT2

PPT3

PPT4

PPT5

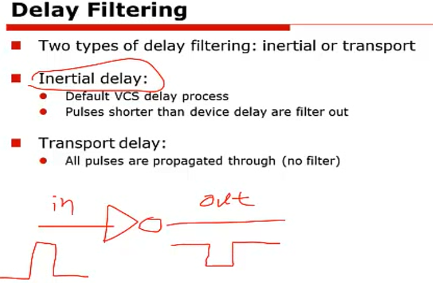

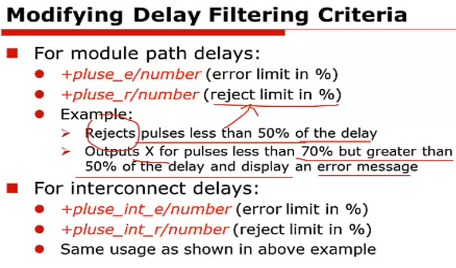

5. 延遲過濾

PPT1

PPT2

慣性延遲:輸入的脈沖寬度需要大於一定量

PPT3

6. 實驗環節

綜合生成網表文件

把DC啟動,並用source跑

更多的關注map下的文件,包括吐出來的fsm_moore.v和fsm_mooere.sdf

前仿真和后仿真

- 設計文件為備份為

fsm_moore.v.bak

備份操作mv fsm_moore.v fsm_moore.v.gate

執行編譯make com

通過dve把.vpd文件打開、前仿真的文件沒有任何延遲毛刺

- 把SDF文件反標的仿真文件

前兩個分別為sdf的絕對路徑和,所對應的模塊

1:1:1意思是延遲乘以的比例,縮放因子

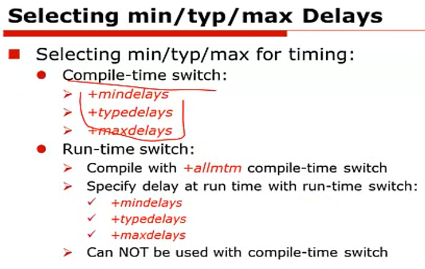

FROM_MTM max min等的延遲

- 對應的makefile

仿真make sim

后仿真由於延遲信息會帶來毛刺信息,如下圖所示