前面讲的都是功能仿真 ,都是理想的仿真,验证代码的功能。

前仿只是完成了一部分。

- 器件自身的延迟

- 连线的延迟

取决于器件的类型,工艺有关。后仿真更加关注toggle的覆盖率

后仿真是十分慢的,门级仿真特别花

1. 课程目标

DC综合之后,得到的网表会将触发器,连线器件的延迟,反标到网表中,都是算法得到的。

怎么样时序信息提取出来后反标

2. 门级验证的流程

PPT1

DC是不含物理信息的

PPT2

PPT3

综合是否保持层次化,视情况而定

3. 门级验证的时序信息

- race命令,把冲突结果放到日志里面

4. 时序信息反标到门级网表

PPT1

把SDF文件反标的仿真文件中,用到了仿真的库

第二种方式

PPT2

PPT3

PPT4

PPT5

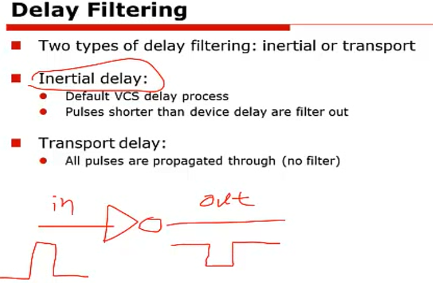

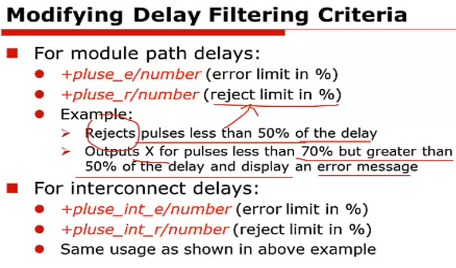

5. 延迟过滤

PPT1

PPT2

惯性延迟:输入的脉冲宽度需要大于一定量

PPT3

6. 实验环节

综合生成网表文件

把DC启动,并用source跑

更多的关注map下的文件,包括吐出来的fsm_moore.v和fsm_mooere.sdf

前仿真和后仿真

- 设计文件为备份为

fsm_moore.v.bak

备份操作mv fsm_moore.v fsm_moore.v.gate

执行编译make com

通过dve把.vpd文件打开、前仿真的文件没有任何延迟毛刺

- 把SDF文件反标的仿真文件

前两个分别为sdf的绝对路径和,所对应的模块

1:1:1意思是延迟乘以的比例,缩放因子

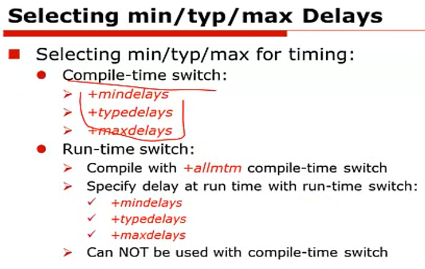

FROM_MTM max min等的延迟

- 对应的makefile

仿真make sim

后仿真由于延迟信息会带来毛刺信息,如下图所示