課前回顧

仿真事件隊列指的是計算機按照一定的順序執行我們的代碼,設計工程師知道一些有關概念,出現了錯誤能夠理解

VCS是一個編譯型的仿真器,編譯得到了二進制可執行文件

1.VCS的Debug

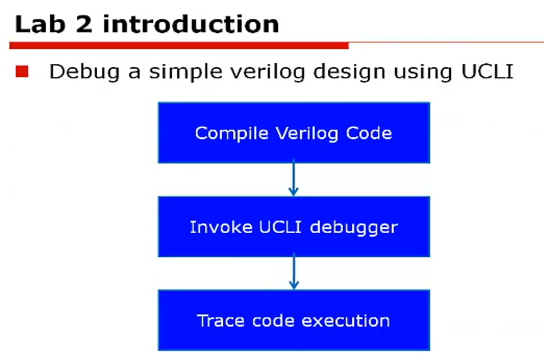

PPT1 課程目標

Unit Objectives

After completing this unit, you should be able to:

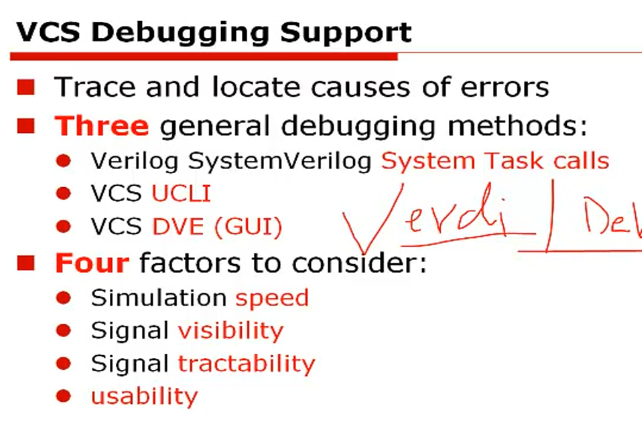

- Describe three methods of debugging Verilog code using VCS

- Invoke UCLI debugger

- Debug Verilog designs using UCLI

PPT2 VCS Debug Support

專業的Debug工具 Verdi(Linux) Debusy(Windows)

開始關注的功能,工程的時候要考慮

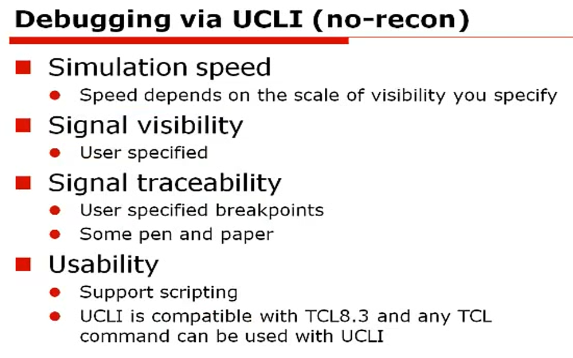

- 速度(開關選項會影響,消耗波形資源,什么級別的仿真,速度上:行為級>RTL級>門級)

- 可見性和可追蹤性(醫生詢問病人,咨詢問題,根據回答定位問題出在哪兒)

- 可用性, 命令行去Debug比較麻煩,DVE比較方便

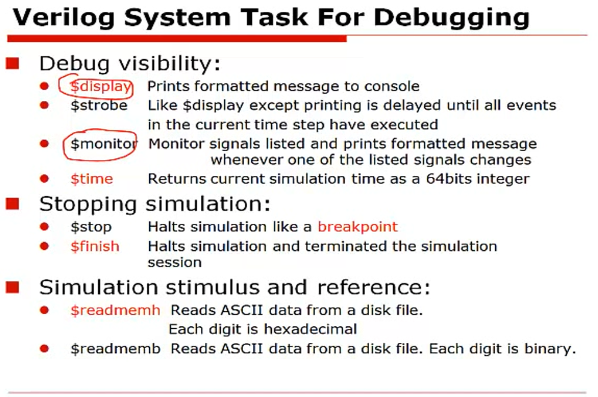

PPT3 Debug系統函數

- display是賦值前的值,monitor是賦值后的值,在的不同區,前者在active區,后者在monitor區

- time是仿真的時間,仿真時間和CPU執行時間

- readmemh讀RAM 讀ROM 讀FIFO,等效為一個數組,將初始化的數據寫在一個文件里,讀取16進制. readmemb讀取二進制的

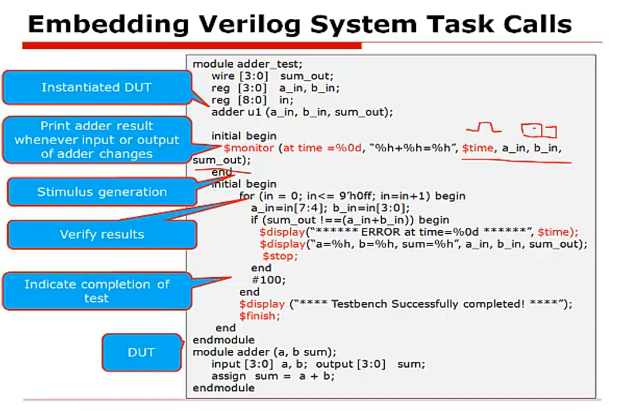

PPT4 嵌入系統函數

包括DUT, DUT的例化,監視輸出信號,激勵的生成,結果的驗證,完成測試(finish,stop)

- stop相當於一個斷點,點run繼續往下跑

- finish相當於仿真已經結束

2.通過命令行(不推薦)

PPT1

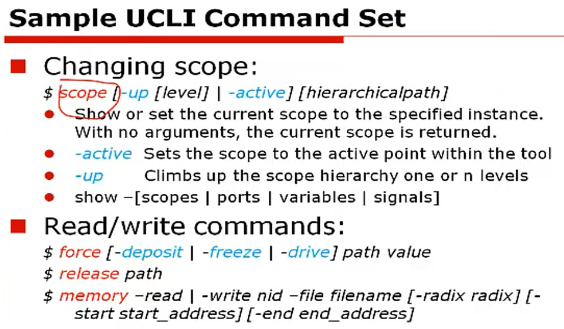

PPT2 編譯調用UCLI Debug

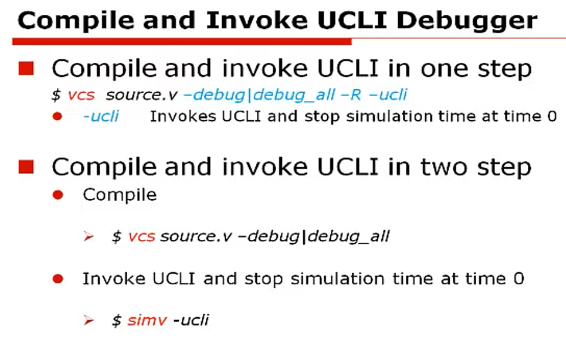

$vcs sorce.v -debug|debug_all|debug_pp -R -ucli # 一步走

# 其他的

VCS的安裝目錄下有相應的手冊

PPT3

PPT4

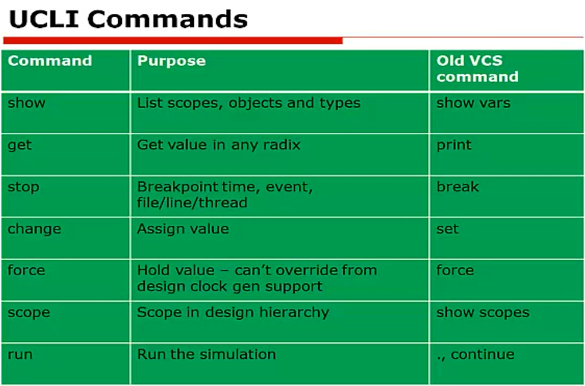

老的命令和新的命令的對比

PPT5

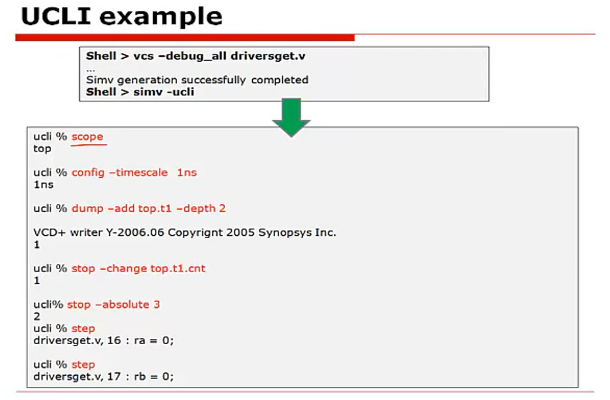

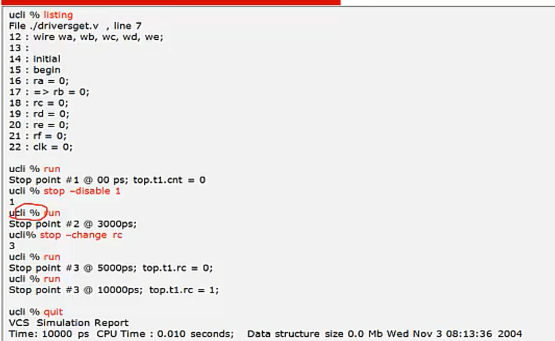

PPT6 使用UCLI的例子

總結:這樣的方法太笨拙了

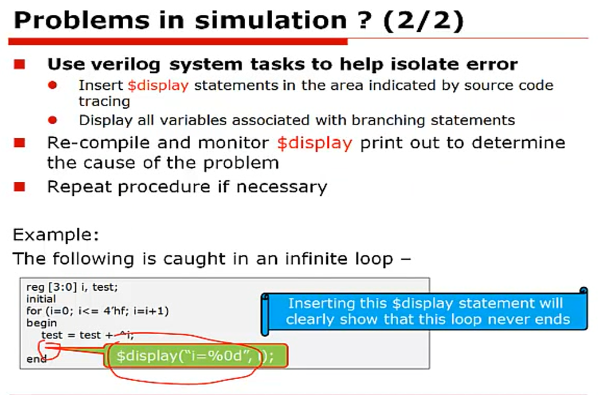

3.仿真時出現的問題

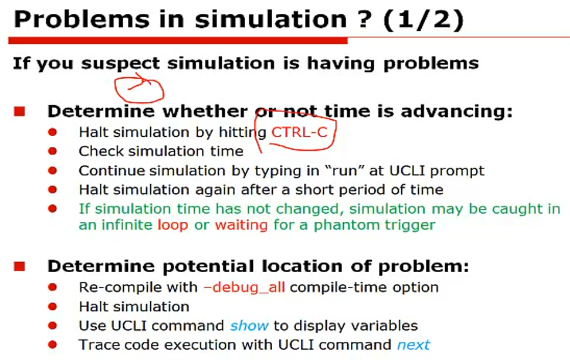

PPT1

出現卡死 殺死進程,發現卡死的仿真時間和對應的代碼

編譯時候加上`debug-all`選項

PPT2

4.利用命令行進行仿真的實驗