大型SoC的設計:大部分時間在做優化,設計,寫代碼是其次。更多的是Debug

衡量仿真的效率:仿真速度快,CPU資源少,內存少

這節課並不是最重要的,但是涉及仿真的高效性和思想

課程目標

- 好的編碼風格

- 利用VCS提供的開關選項, +rad開關

工具其實有限的,最重要的是人的設計

1. 仿真的效率

PPT1

- 適當的選擇開關選項

- 三個小問題改完了再去編譯,而不是蓋一個編譯一次,門級仿真編譯更慢

PPT2 VCS的架構

VCS處理代碼的過程

第一遍就考慮把事情做好,一氣呵成

2. 通用代碼建議

PPT1

- 可綜合Verilog語法集

- 提升你的抽象層次,RTL級>門級>原語級。后仿真(門級)的速度很慢,適當的用狀態機

- 避免效率的低的語句,原語級,雙向口

- 使用小的激勵塊,module不要寫的太大,不利用維護,激勵多用task去包裝。

- 使用基於文本的激勵輸入readmemh,是否dump數組到波形

readmenh和writemenh用的最多,最后把結果保存到文本文件中

PPT2

在設計里面避免

PPT3

- 避免門級結構 (gate-level UDP)

- 數據類型,常用reg wire 和integer

- 跨模塊的引用

3. VCS優化代碼方法

PPT1

PPT2 使用rad優化的例子1

PPT3 使用rad優化例子2

PPT4

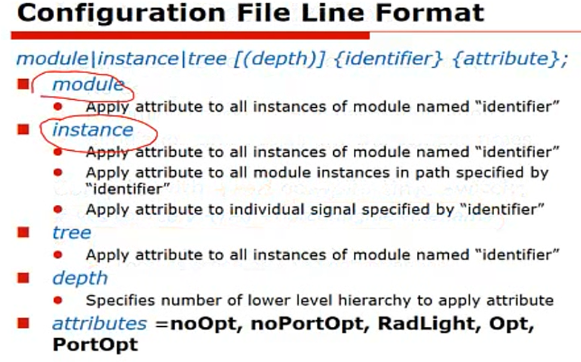

PPT5 配置文件

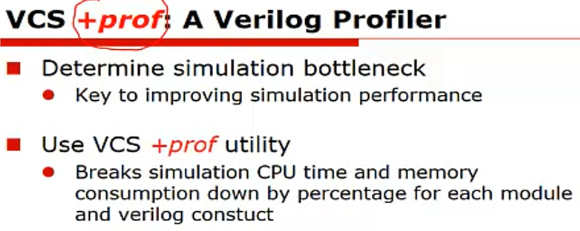

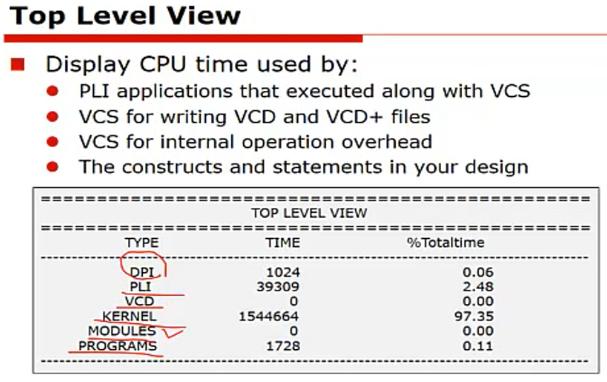

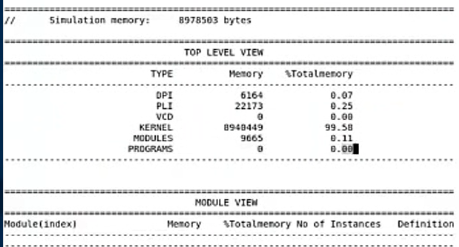

4. prof性能分析

PPT1

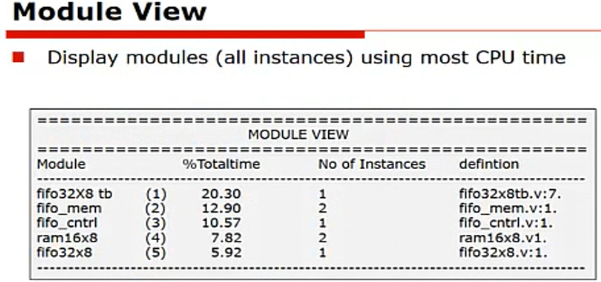

統計分析哪個模塊占用資源比較多

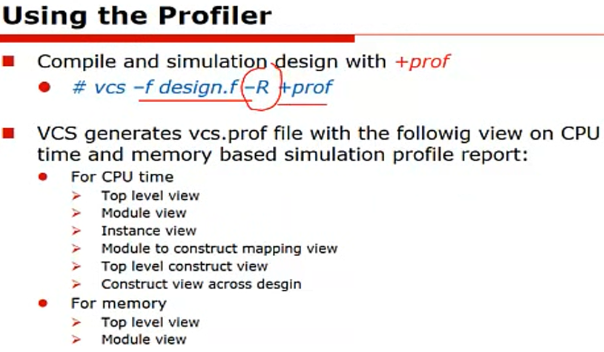

PPT2

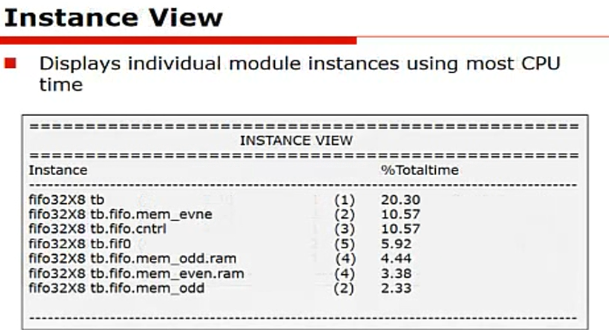

PPT3

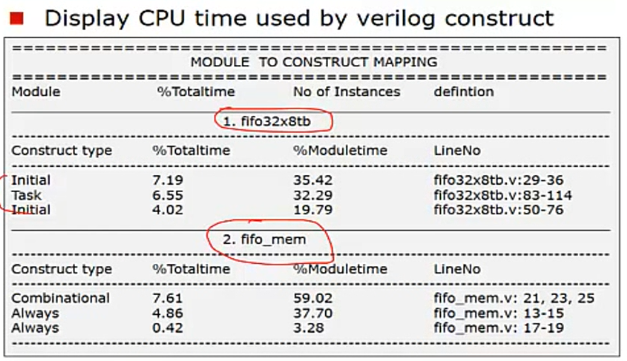

PPT4 報告的內容

PPT5

5. 實驗環節

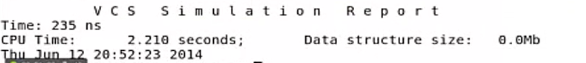

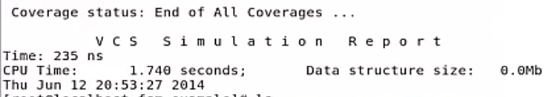

- 沒有加的仿真時間

加上了+rad的仿真時間

- 加上了編譯型的開關

+prof,多出了vcs.prof文件

warning可以看看,有幫助

性能分析,往往是針對大型的項目

gVim下刪除一行的快捷鍵的連線敲兩個d

-

+prof未來的版本不支持該命令改用+simprofile -

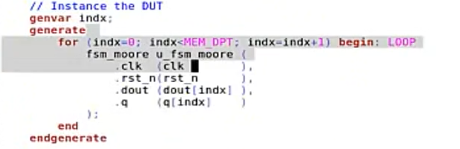

例化多個模塊,

generate例化module是不能用數組的

例如1000個計數器下

后面講了

后面講了 -

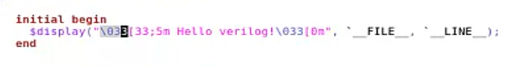

打印出帶顏色的字體