3.1 總線的基本概念

-

為什么要用總線

計算機系統五大部件之間的互連方式有兩種:

- 分散連接——各部件之間使用單獨的連線

- 總線連接——各部件連到一組公共信息傳輸線上

早期的計算機大多采用分散連接方式,內部連線十分復雜,尤其當I/O與存儲器交換信息時都需要經過運算器,使運算器停止運算,嚴重影響CPU的工作效率。

-

什么是總線

總線是連接各個部件的信息傳輸線,是各個部件共享的傳輸介質

-

總線上的信息傳送

- 串行

- 並行

3.2 總線的分類

-

片內總線

芯片內部的總線

- CPU芯片內部

- 寄存器之間

- 寄存器與算邏單元ALU之間

-

系統總線

計算機各部件(CPU、主存、I/O設備)之間的信息傳輸線

按系統總線傳輸信息不同分為:

- 數據總線——傳輸各功能部件之間的數據信息

- 雙向

- 與機器字長、存儲字長有關

- 數據總線寬度——數據總線的位數

- 地址總線——用來指出數據總線上的源數據或目的數據在主存單元的地址或I/O設備的地址

- 單向(由CPU輸出)

- 與存儲地址、I/O地址有關

- 地址線位數(\(2^n\))與存儲單元的個數(n)有關

- 控制總線——用來發出各種控制信號的傳輸線

- 出——中斷請求、總線請求

- 入——存儲器讀/寫、總線允許、中斷確認

- 常見控制信號:

- 時鍾:用來同步各種操作

- 復位:初始化所有部件

- 總線請求:表示某部件需獲得總線使用權

- 總線允許:表示需要獲得總線使用權的部件已獲得了控制權

- 中斷請求:表示某部件提出中斷申請

- 中斷響應:表示中斷請求已被接收

- 存儲器寫:將數據總線上的數據寫至存儲器的指定地址單元內

- 存儲器讀:將指定存儲單元中的數據讀到數據總線上

- I/O讀:從指定的I/O端口將數據讀到數據總線上

- I/O寫:將數據總線上的數據輸出到指定的I/O端口內

- 傳輸響應:表示數據已被接收,或已將數據送至數據總線上

- 數據總線——傳輸各功能部件之間的數據信息

-

通信總線

用於計算機系統之間或計算機系統與其它系統(控制儀器、移動通信等)之間的通信

通信方式:

- 串行通信

- 數據在單條1位寬的傳輸線上,一位一位地按順序分時傳送。

- 一字節的數據要通過一條傳輸線分8次由低位到高位按順序傳送

- 適用於遠距離傳送,實現遠程通信

- 數據在單條1位寬的傳輸線上,一位一位地按順序分時傳送。

- 並行通信

- 數據在多條並行1位寬的傳輸線上,同時由源傳送到目的地。

- 一字節的數據要通過8條並行傳輸線同時由源傳送到目的地

- 適宜於近距離的數據傳輸,通常小於30m

- 數據傳送速率與距離成反比

- 串行通信

3.3 總線特性及性能指標

-

總線物理實現

總線由許多導線直接印制在電路板上,延伸到各個部件。

CPU、主存、I/O這些插板通過插頭與水平方向總線插槽連接。為了保證機械上的可靠連接,必須規定其機械特性;為了確保電氣上的正確連接,必須規定其電氣特性;為了保證正確地連接不同部件,還需規定其功能特性和時間特性。

Pentium Ⅲ以上微型計算機已將CPU芯片直接安裝在主板上,很多插卡已做成專用芯片,減少插槽,結構更合理。

-

總線特性

-

機械特性——總線在機械連接方式上的一些性能

- 尺寸

- 形狀

- 管腳數

- 排列順序

-

電氣特性

- 每一根傳輸線上信號的傳輸方向

- 有效電平范圍

-

功能特性——每根傳輸線的功能

- 地址

- 數據

- 控制

-

時間特性——信號的時序關系

- 總線中的任一根線在什么時間內有效

- 每條總線上的各種信號互相存在一種有效時序關系,一般可用信號時序圖描述

-

-

總線的性能指標

- 總線寬度

- 數據線的根數

- 用bit(位)表示(8位,16位,32位,64位)

- 標准傳輸率——每秒傳輸的最大字節數\(-MBps\)

- 時鍾同步/異步——同步/不同步

- 總線復用——地址線與數據線復用

- 信號線數——\(\bold{地址線+數據線+控制線}\)

- 總線控制方式

- 突發工作

- 自動配置

- 仲裁方式

- 邏輯方式

- 計數方式

- 其他指標

- 負載能力

- 電源電壓

- 總線寬度能否擴展

- 總線寬度

-

總線標准

總線標准 數據線 總線時鍾 帶寬 ISA

工業標准結構總線16 8MHz(獨立) 16MBps EISA

擴展工業標准結構32 8MHz(獨立) 33MBps VESA(VL-BUS)

視頻電子標准協會32 32MHz(CPU) 132MBps PCI

外設部件互聯標准32/64 33MHz(獨立)/ 66MHz(獨立) 132MBps

528MBpsAGP

加速圖形接口32 66.7MHz(獨立)

133MHz(獨立)266MBps

533MBpsRS-232 串行通信總線標准 數據終端設備(計算機)和數據通信設備

(調制解調器)之間的標准接口USB

通用串行總線串行通信總線標准 普通無屏蔽雙絞線

帶屏蔽雙絞線

最高1.5MBps (USB1.0)

12MBps (USB1.0)

480MBps (USB2.0)

3.4 總線結構

-

單總線結構

-

多總線結構

-

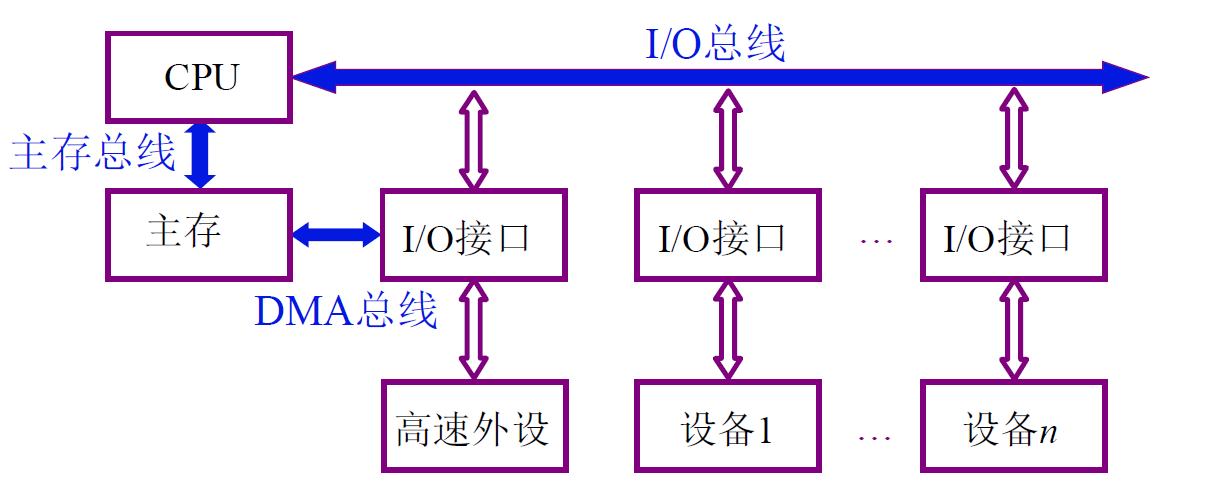

雙總線結構(分離主存總線和I/O主線)

-

三總線結構

DMA(主存與I/O設備之間):直接存儲器訪問

-

三總線結構2

多種外部設備都連在一條擴展總線上,影響外設設備工作速度

-

四總線結構

分離高速設備和低速設備

-

-

總線結構舉例

-

傳統微型機總線結構

分離系統總線和I/O總線

-

VL-BUS局部總線結構

分類組織高速設備和低速設備

-

PCI 總線結構

-

多層 PCI 總線結構

-

3.5 總線控制

-

總線判優控制

- 主設備(模塊)——對總線有控制權

- 從設備(模塊)——響應從主設備發來的總線命令

- 某些設備既可作為主設備也可作為從設備

\[控制方法\begin{cases} 集中式\begin{cases} 鏈式查詢\\ 計數器定時查詢\\ 獨立請求方式 \end{cases}\\ 分布式 \end{cases} \] -

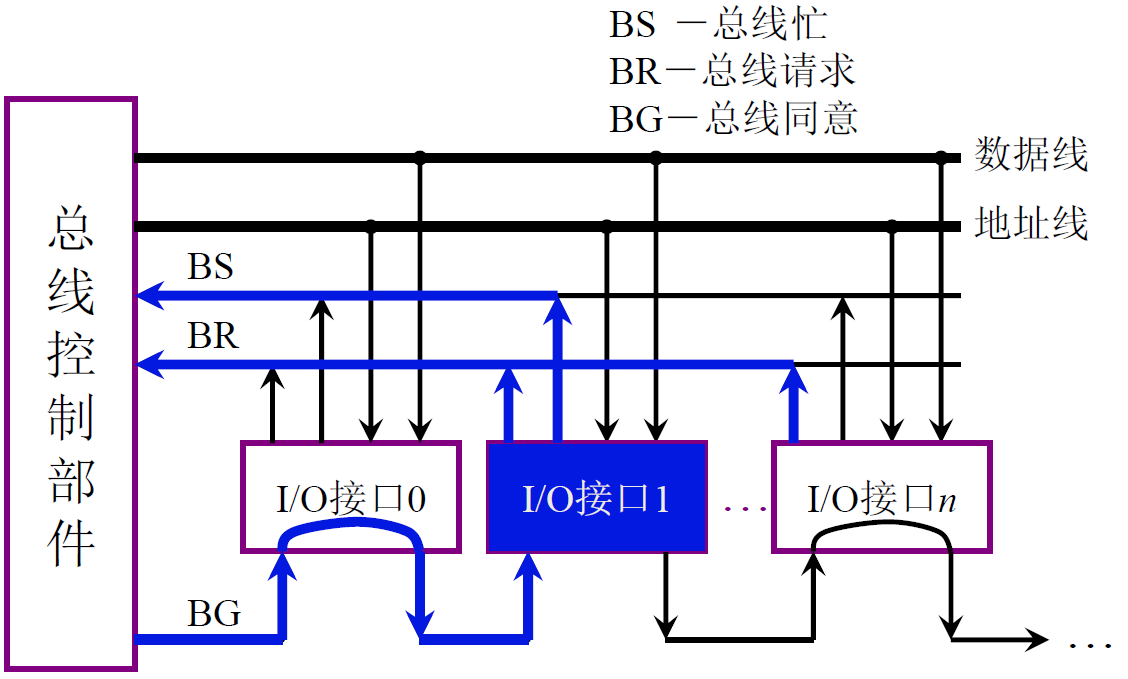

集中式查詢

-

鏈式查詢

- 優先級由連接方式事先決定\(\implies\)BG的查詢順序

- 增添設備容易

- 容易實現可靠性設計

- 速度慢\(\implies\)用於微型計算機,嵌入式系統

- 對電路故障敏感(尤其BG線)

-

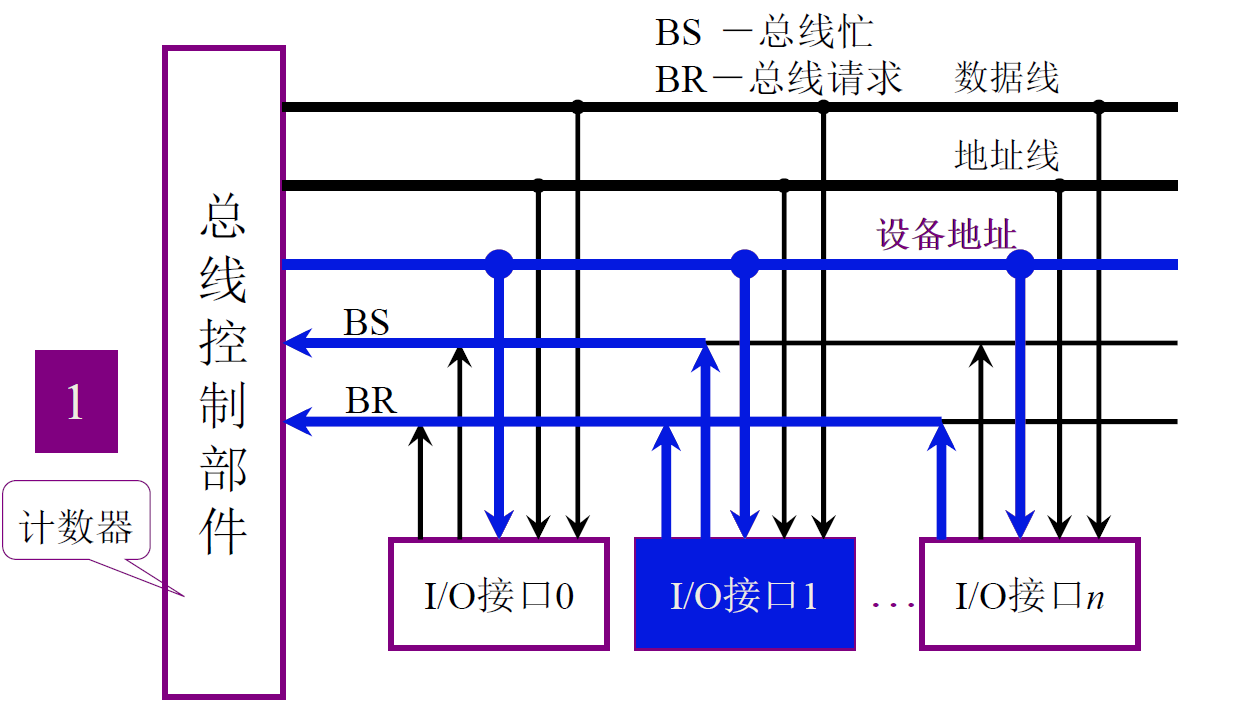

計數器定時查詢

-

判優過程:計數器控制設備地址線進行查詢

-

設備地址線寬度:與設備數n有關\(\implies\lceil\log_{2}{n}\rceil+2\)

-

判優靈活:可設定計數器初值;利用循環計數實現公平判優

-

-

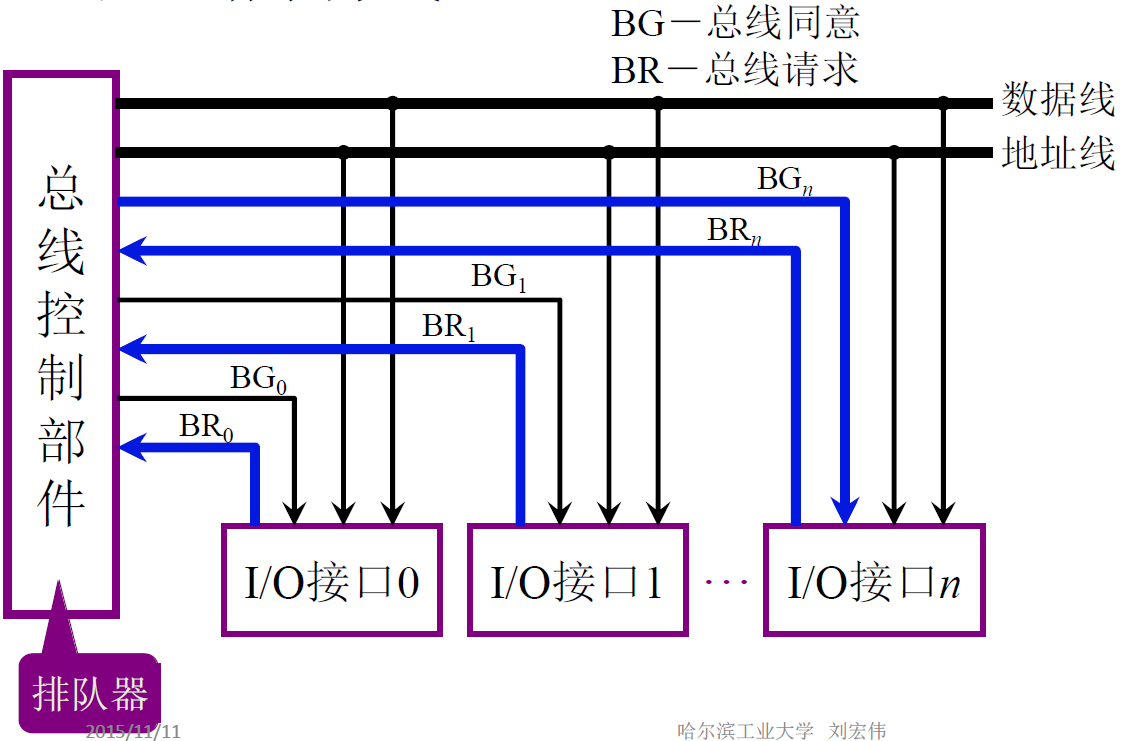

獨立請求方式

-

速度更快

-

每個I/O接口都有單獨的請求線和授權線

-

優先級:總線控制部件內部有排隊器

-

線數多:\(2^n\)

-

-

-

總線通信控制

- 目的:解決通信雙方協調配合的問題

- 總線傳輸周期

- 申請分配階段:主模塊申請,總線仲裁決定

- 尋址階段:主模塊向從模塊給出地址和命令

- 存數階段:主模塊和從模塊交換信息

- 結束階段:主模塊撤消有關信息

- 總線通信的四種方式

\[\begin{cases} \text{同步通信}\quad\quad由\color{blue}{統一時標}\color{black}控制數據傳送\\ \text{異步通信}\quad\quad采用\color{blue}{應答方式}\color{black},沒有公共時鍾標准\\ \text{半同步通信}\quad\,\color{blue}同步、異步結合\\ \text{分離式通信}\quad\,充分\color{blue}挖掘\color{black}系統\color{blue}總線每個瞬間\color{black}的\color{blue}潛力 \end{cases} \] -

同步通信——定寬定距的公共時鍾信號

-

優點

- 規定明確、統一

- 模塊間的配合簡單一致

-

缺點

- 主、從模塊時間配合“強制性”同步

- 必須按最慢速度的部件來設計公共時鍾,嚴重影響總線的工作效率

-

一般用於總線長度較短,各部件存取時間比較一致的場合

- 總線傳輸周期越短,數據線的位數越多,直接影響總線的數據傳輸率

-

同步式數據輸入

- \(T_1\)上升沿主設備給出地址信號

- \(T_2\)上升沿給出讀命令信號

- \(T_3\)上升沿從設備給出數據信號(數據總線)

- \(T_4\)上升沿撤銷數據信號和控制信號

- \(T_4\)下降沿撤銷地址信號

-

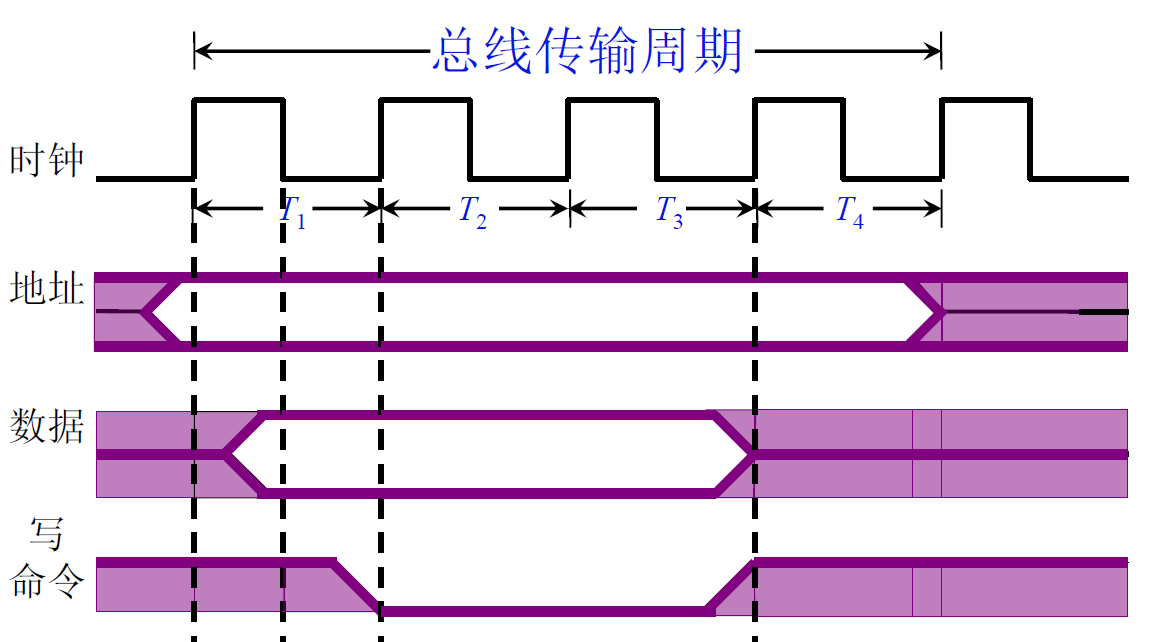

同步式數據輸出

- \(T_1\)上升沿給出地址信號

- \(T_1\)下降沿給出數據

- \(T_2\)上升沿給出寫命令

- \(T_3\)上升沿執行寫操作

- \(T_4\)上升沿撤銷數據和寫命令

- \(T_4\)下降沿撤銷地址數據

數據傳輸率:每秒傳輸的最大字節數——\(MBPs\)

例1:假設總線的時鍾頻率為\(100MHz\),總線的傳輸周期為4個時鍾周期,總線的寬度為32位,試求總線的數據傳輸率。若想提高一倍的數據傳輸率,可采取什么措施?

解:根據總線時鍾頻率為\(100MHz\),得

一個時鍾周期為\(\frac{1}{100}MHz=0.01\mu s\)

總線傳輸周期為\(0.01\mu s\times4=0.04\mu s\)

由於總線得寬度為\(32位=4B(字節)\)

\(\implies\)總線的數據傳輸率為\(\frac{4B}{0.04\mu s}=100 MBps\)

若想提高一倍數據傳輸率,可以在不改變總線時鍾頻率得前提下,將數據線得寬度改為64位;

也可以保持32位的數據寬度,讓總線的時鍾頻率增加到\(200MHz\)

-

-

異步通信

\[\begin{cases} \text{主設備}\quad發起總線通訊\\ \text{從設備}\quad受主設備控制 \end{cases}\\ 增加\begin{cases} \text{請求線}\\ \text{應答線} \end{cases} \]-

不互鎖

- 主設備發出通信請求

- 從設備收到請求后進行應答

- 主設備撤銷請求信號

- 從設備撤銷應答信號

無論從設備是否收到請求信號,一段時間后主設備都會撤銷請求信號

無論主設備是否收到應答信號,一段時間后從設備都會撤銷應答信號

\(\implies\) 通信可靠性存在問題

-

半互鎖

- 主設備發出通信請求

- 從設備收到請求后進行應答

- 主設備收到應答后撤銷請求信號

- 從設備撤銷應答信號

只有收到應答后主設備才撤銷請求信號

無論主設備是否收到應答信號,一段時間后從設備都會撤銷應答信號

\(\implies\)可能造成主設備請求信號一直保持高電平

-

全互鎖

- 主設備發出通信請求

- 從設備收到請求后進行應答

- 主設備收到應答后撤銷請求信號

- 請求信號撤銷后從設備撤銷應答信號

異步串行通信的數據傳送速率:

- 波特率:單位時間內傳送二進制數據的位數——\(bps(位/秒)\)

- 比特率:單位時間內傳送二進制有效數據的位數——\(bps(位/秒)\)

例2:在異步串行傳輸系統中,假設每秒傳輸120個數據幀,其字符串格式規定包含1個起始位,7個數據位,1個奇校驗位、1個終止位,試計算波特率。

解:根據題目給出的字符格式,一幀包含\(1+7+1+1=10位\)

\(\implies\)波特率為\((1+7+1+1)\times120=1200bps=1200波特\)

例3:在異步串行傳輸系統中,若字符串格式為:1起始位、8位數據位、1位奇校驗位、1位終止位。假設波特率為\(1200bps\),求此時的比特率。

解:總數據位:\(1+8+1+1=11位\)

有效數據位:8位

\(\implies\)比特率為\(1200\times\frac{8}{11}\approx872.72bps\)

-

-

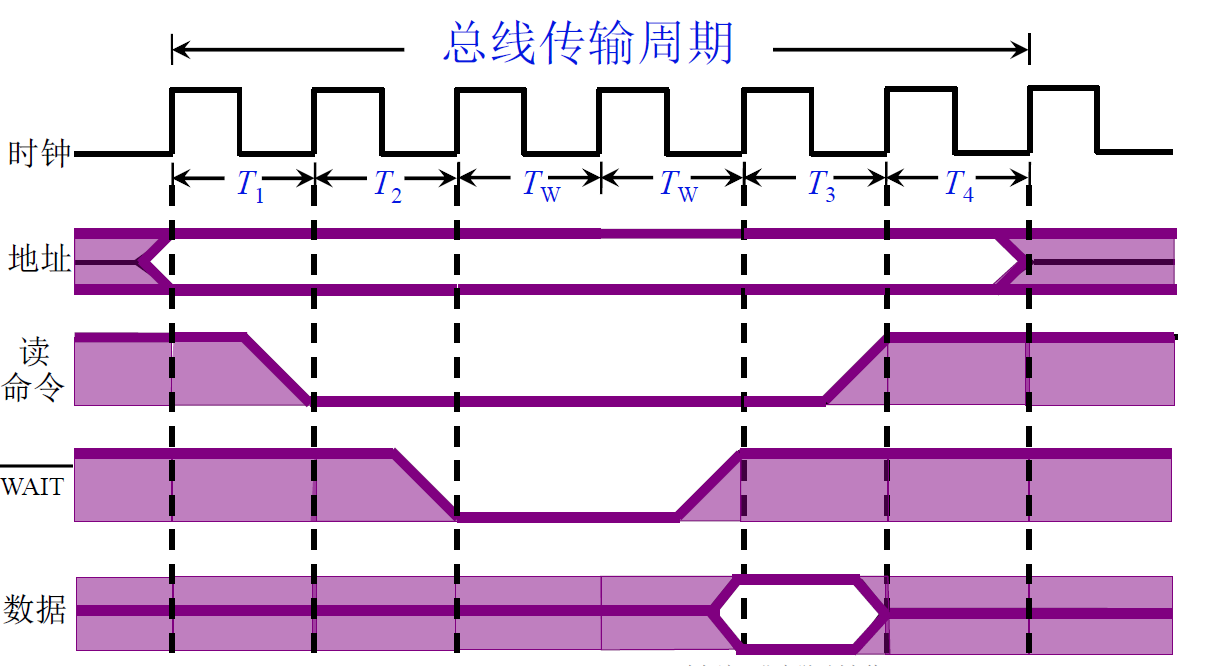

半同步通信

- 同步特征

- 發送方用系統時鍾前沿發信號

- 接收方用系統時鍾后沿判斷、識別

- 異步特征

- 允許不同速度模塊和諧工作

- 增加一條“等待”響應信號\(\to\overline{WAIT}\)

- 例:輸入數據

- \(T_1\) 主設備發地址

- \(T_2\) 主設備發命令

- \(T_W\) 當\(\overline{WAIT}\)為低電平時,等待一個\(T\)

- \(T_W\) 當\(\overline{WAIT}\)為低電平時,等待一個\(T\)

- ......

- \(T_3\) 從設備提供數據

- \(T_4\) 從設備撤銷數據,主模塊撤銷命令

上述三種通信的共同點:

一個總線傳輸周期(以輸入數據為例):

- 主模塊發地址、命令\(\to\)占用總線

- 從模塊准備數據\(\to\)不占用總線\(\implies\)總線空閑

- 從模塊向主模塊發數據\(\to\)占用總線

- 同步特征

-

分離式通信

- 各模塊有權申請占用總線

- 采用同步方式通信,不等對方回答

- 各模塊准備數據時,不占用總線

- 總線被占用時,無空閑

\(\implies\)充分提高了總線的有效占用

一個總線傳輸周期:

- 子周期1——主模塊申請占用總線,使用完后即放棄總線的使用權

- 子周期2——從模塊(此時相當於主模塊)申請占用總線,將各種信息送至總線上

分離式通信控制比較復雜,一般在普通微型計算機系統很少采用