單總線接口簡介

概述

單總線及相應芯片是美國Dallas Semiconductor公司近年推出的新技術,也稱為I-Wire總線結構。單總線系統定義了一根信號線,總線上的每個器件都能夠在合適的時間驅動它,相當於把計算機的地址線、數據線、控制線合為一根信號線對外進行數據交換而無須時鍾同步線。目前,已有多種器件選用單總線結構,如A/D轉換器、D/A轉換器、溫度傳感器等。

單總線技術作用距離在單片機I/O直接驅動下可達200m,經擴展可達1000m以上。使用單總線結構可以大大簡化電路設計,節約引腳的使用,允許掛上百個器件,能滿足一般測控系統的要求,如環境狀態檢測系統、實時氣象監測系統(自動氣象站)、軍用倉庫測控系統、農業塑料大棚測控系統、賓館樓宇監管系統、停車收費系統、考勤管理系統等領域的應用開發。單總線的數據傳輸有兩種模式,通常以16.3Kbps的速率通信,超速模式可達142Kbps。因此,只能用於對速度要求不高的場合,一般用於100Kbps以下速率的測控或數據交換系統中。

硬件結構及配置

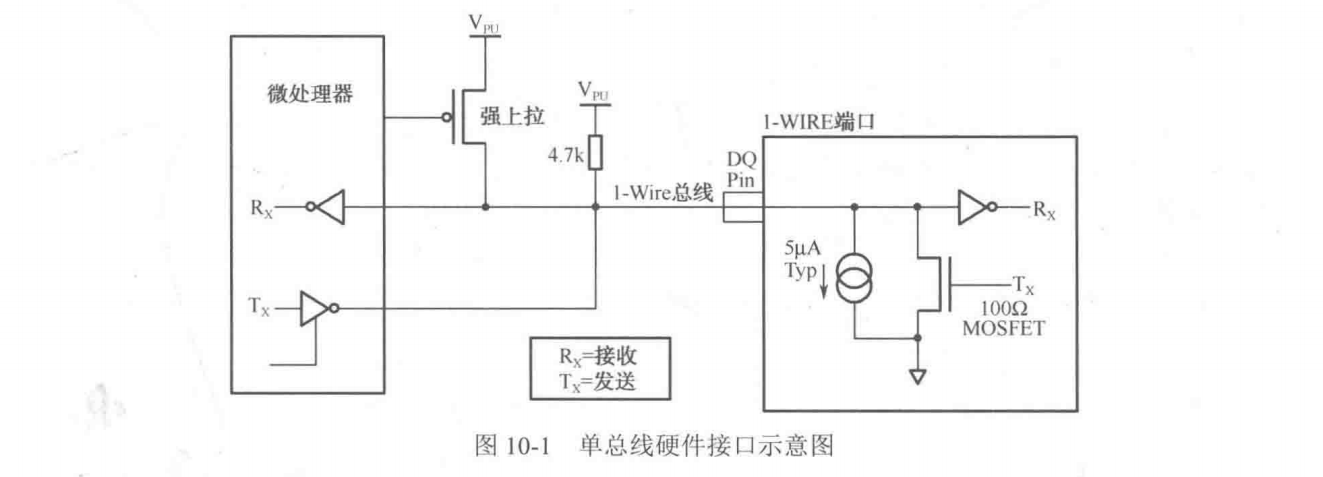

單總線只有一根數據線,設備、主機或從機通過一個漏極開路或三態端口連接至該數據線,這樣允許設備在不發送數據時釋放數據總線,以便總線被其他設備所使用,單總線端口為漏極開路,其內部等效電路如圖10-1所示。

單總線要求外接一個約5千歐的上拉電阻,以滿足單總線的閑置狀態為高電平的要求。不管什么原因,如果傳輸過程需要暫時掛起,且要求傳輸過程還能夠繼續的話,則總線必須處於空閑狀態。位傳輸之間的恢復時間沒有限制,只要總線在恢復期間處於空閑狀態(高電平),如果總線保持低電平超過480us,總線上的所有器件將復位。另外,在寄生方式供電時,為了保證單總線器件在某些工作狀態下(如溫度轉換期間E2PROM寫入等)具有足夠的電源電流,必須在總線上提供強上拉(如圖10-1所示的MOSFET)。

命令序列

單片機系統中配置的各種器件,由Dallas公司提供專用芯片。每個芯片都有64位ROM,從最低位開始,前8位是族碼,表示產品的分類編號;接着的48位是一個唯一的序列號;最后8位是CRC校驗碼。典型的單總線命令序列如下。

- 初始化

初始化過程由主機發出的復位脈沖和從機響應的應答脈沖組成。應答脈沖使主機知道總線上有從機設備且准備就緒。 - ROM命令

讀ROM命令、匹配ROM命令、搜索ROM命令、報警搜索命令、跳躍ROM命令。這些命令與各個從機設備的唯一 64位ROM相關,允許主機在單總線上連接多個從機設備時,指定操作某個從機設備,還允許主機能夠檢測到總線上有多少個從機設備以及其設備類型。 - 功能命令(以DS18B20為例)

在主機發出ROM命令后,可以訪問某個指定的DS18B20,接着就可以發出支持的某個功能命令,這些命令允許主機寫入或讀出DS18B2O暫存器、啟動溫度轉換以及判斷從機的供電方式。

信號方式

所有的單總線器件要求采用嚴格的通信協議,以保證數據的完整性。該協議定義了幾種信號類型:復位脈沖、應答脈沖、寫0、寫1、讀0和讀1。所有這些信號,除了應答脈沖以外,都由主機發出同步信號,並且發送所有的命令和數據都是字節的低位在前,這一點與多數串行通信格式不同,多數為字節的高位在前。

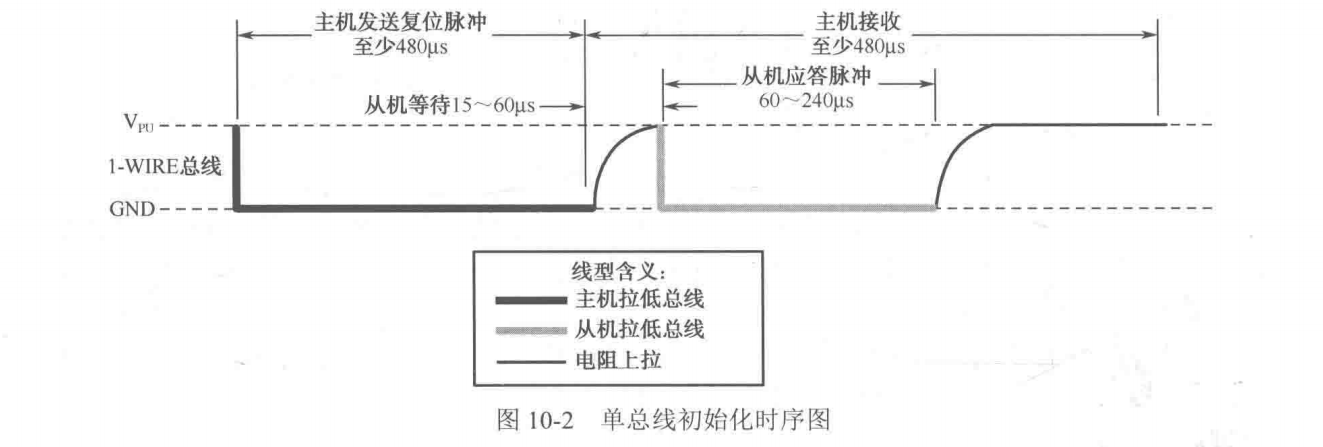

- 初始化序列(復位和應答脈沖)

單總線上的所有通信都是以初始化序列開始的,包括:主機發出的復位脈沖及從機的應答脈沖,如圖10-2所示。當從機發出響應主機的應答脈沖時,即向主機表明它處於總線上,且工作准備就緒。在主機初始化過程,主機通過拉低單總線至少48us,以產生(Tx)復位脈沖。接着,主機釋放總線,並進入接收模式(Rx)。當總線被釋放后5千歐上拉電阻將單總線拉高,在單總線器件檢測到上升沿后,延時15〜60us,接着通過拉低總線60〜240us,以產生應答脈沖。

-

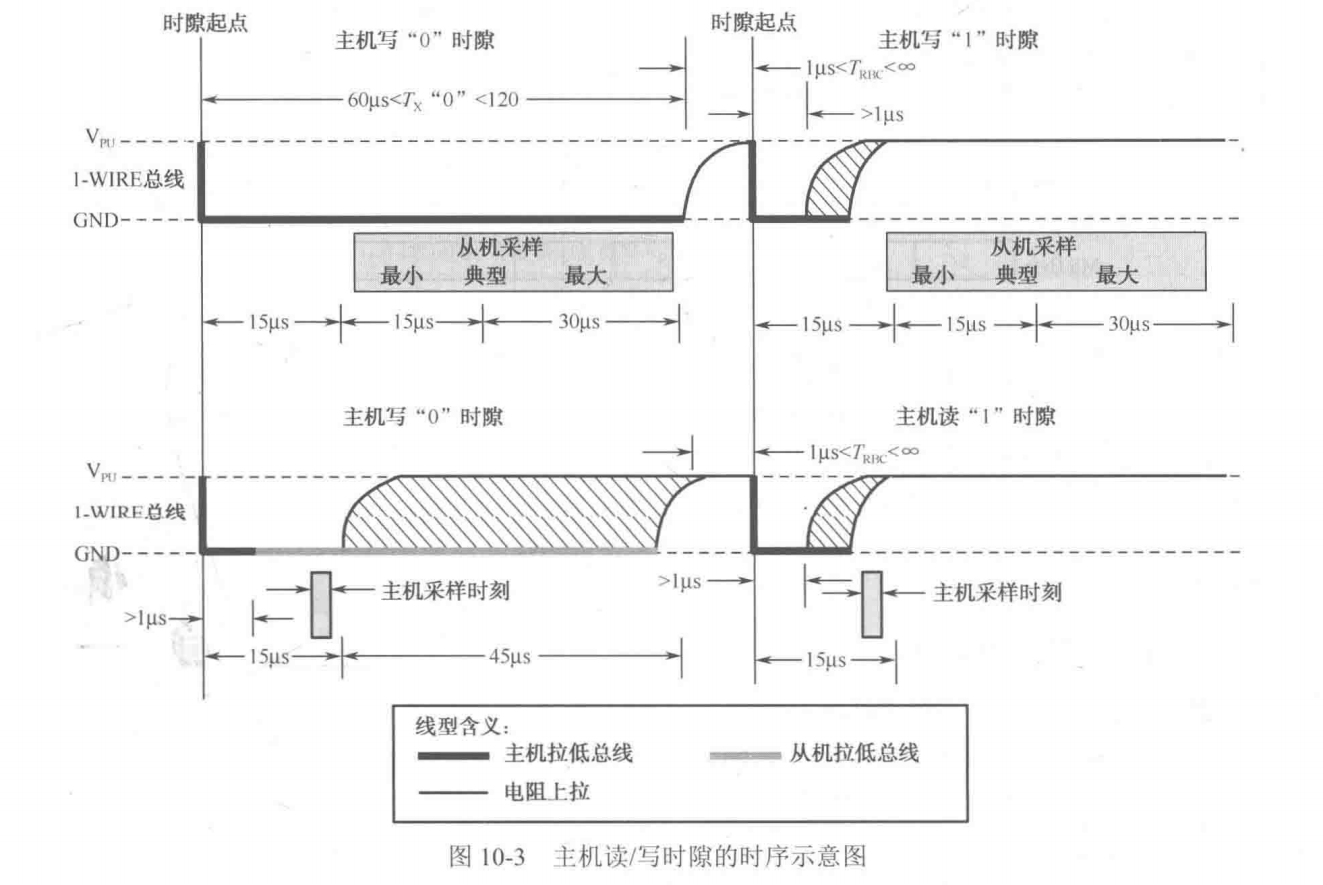

讀/寫時隙

在寫時隙期間,主機向單總線器件寫入數據,而在讀時隙期間,主機讀入來自從機的數據,在每一個時隙,總線只能傳輸一位數據。存在兩種寫時隙,寫1和寫0。主機釆用寫1時隙向從機寫入1,而釆用寫0時隙向從機寫入0。所有寫時隙至少需要60us,且在兩次獨立的寫時隙之間至少需要1us的恢復時間。兩種寫時隙均起始於主機拉低總線。

產生寫1時隙的方式:主機在拉低總線后,接着必須在15us之內釋放總線,由5千歐上拉電阻將總線拉至高電平;

而產生寫0時隙的方式:在主機拉低總線后,只需在整個時隙期間保持低電平即可(至少60us)。

在寫時隙起始后15〜60us期間,單總線器件釆樣總線電平狀態,如果在此期間釆樣為高電平,則邏輯1被寫入該器件;如果為0,則寫入邏輯0。

單總線器件僅在主機發出讀時隙時,才向主機傳輸數據,所以,在主機發出讀數據命令后,必須馬上產生讀時隙,以便從機能夠傳輸數據。所有讀時隙至少需要60us,且在兩次獨立的讀時隙之間至少需要1us的恢復時間。每個讀時隙都由主機發起,至少拉低總線1us。在主機發起讀時隙之后,單總線器件才開始在總線上發送0或1。若從機發送1,則保持總線為高電平;若發送0,則拉低總線。當發送0時,從機在該時隙結束后釋放總線,由上拉電阻將總線拉回至空閑高電平狀態。從機發出的數據在起始時隙之后,保持有效時間15us,因而,主機在讀時隙期間必須釋放總線,並且在時隙起始后的15us之內釆樣總線狀態。

主機讀/寫時隙的時序示意圖如圖10-3所示。

SPI總線拓展技術

SPI總線概述

SPI (Serial Peripheral Interface,串行外設接口)是摩托羅拉公司推出的一種同步串行通信接口,用於微處理器和外圍擴展芯片之間的串行連接,現已發展成為一種工業標准。目前,各半導體公司推出了大量的帶有SPI接口的具有各種功能的芯片,如RAM、E2PROM. Flash ROMsA/D轉換器、D/A轉換器、LED/LED顯示驅動器、I/O接口芯片、實時時鍾、UART收發器等,為用戶的外圍擴展提供了極其靈活而價廉的選擇。

由於SPI總線接口只占用微處理器4個I/O接口地址,釆用SPI總線接口可以簡化電路沒計,節省很多常規電路中的接口器件和I/O 口,提高設計的可靠性。

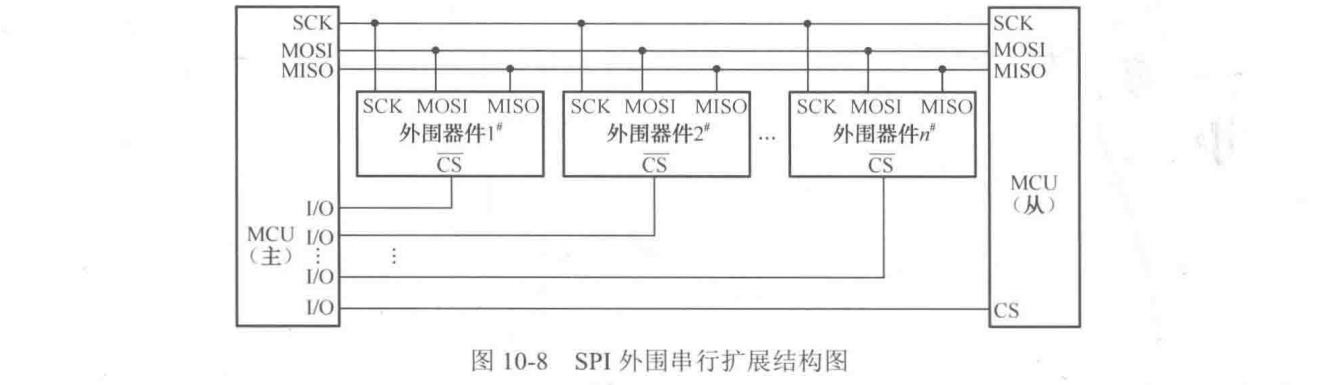

SPI總線結構由一個主設備和一個或多個從設備組成,主設備啟動一個與從設備的同步通信,從而完成數據的交換。SPI接口由MISO (主機輸入/從機輸出數據線)、MOSI (主機輸出/從機輸入數據線)、SCK (串行移位哩)、CS (從機使能信號)4種信號構成,CS決定了唯一的與主設備通信的從設備,如沒有CS信號,則只能存在一個從設備,主設備通過產生移位時鍾來發起通信。

通信時,數據由MOSI輸出、MISO輸入,數據在時鍾的上升或下降沿由MOSI輸出,在緊接着的下降或上升沿由MISO讀入,這樣經過8/16次時鍾的改變,完成8/16位數據的傳輸。其典型系統框圖如圖10-8所示。

在SPI傳輸中,數據是同步進行發送和接收的,由於數據傳輸的時鍾基於來自主處理器的時鍾脈沖,因此SPI傳輸速度大小取決於SPI硬件,其波特率最高可以達到5Mbps。SPI總線主要特點如下:

- SPI是全雙工通信方式,即主機在發送的同時也在接收數據:

- SPI設備既可以當作主機使用,也可以作為從機工作;

- SPI的通信頻率可編程,即傳送的速率由主機編程決定:

- 發送結束中斷標志:

- 數據具有寫沖突保護功能:

- 總線競爭保護等。

SPI總線的數據傳輸方式

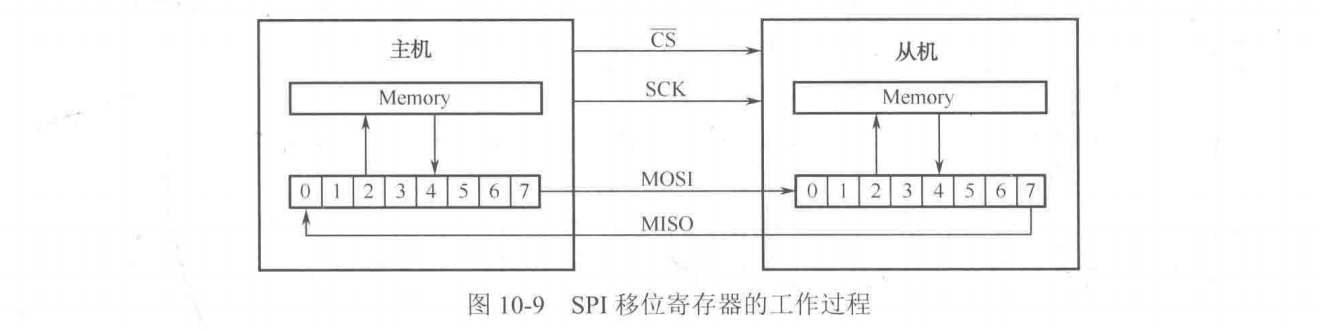

SPI是一種高速的、全雙工、同步的通信總線。主機和從機都有一個串行移位寄存器,主機通過向它的SPI串行寄存器寫入一個字節來發起一次傳輸。寄存器通過MOSI信號線將字節傳送給從機,從機也將自己的移位寄存器中的內容通過MISO信號線返回給主機,如圖10-9所示,兩個移位寄存器形成一個內部芯片環形緩沖器。這樣,兩個移位寄存器中的內容就被交換。外設的寫操作和讀操作是同步完成的。

如果只進行寫操作,主機只需忽略接收到的字節;反之,若主機要讀取從機的一個字節,就必須發送一個空字節來引發從機的傳輸。

SPI接口時序

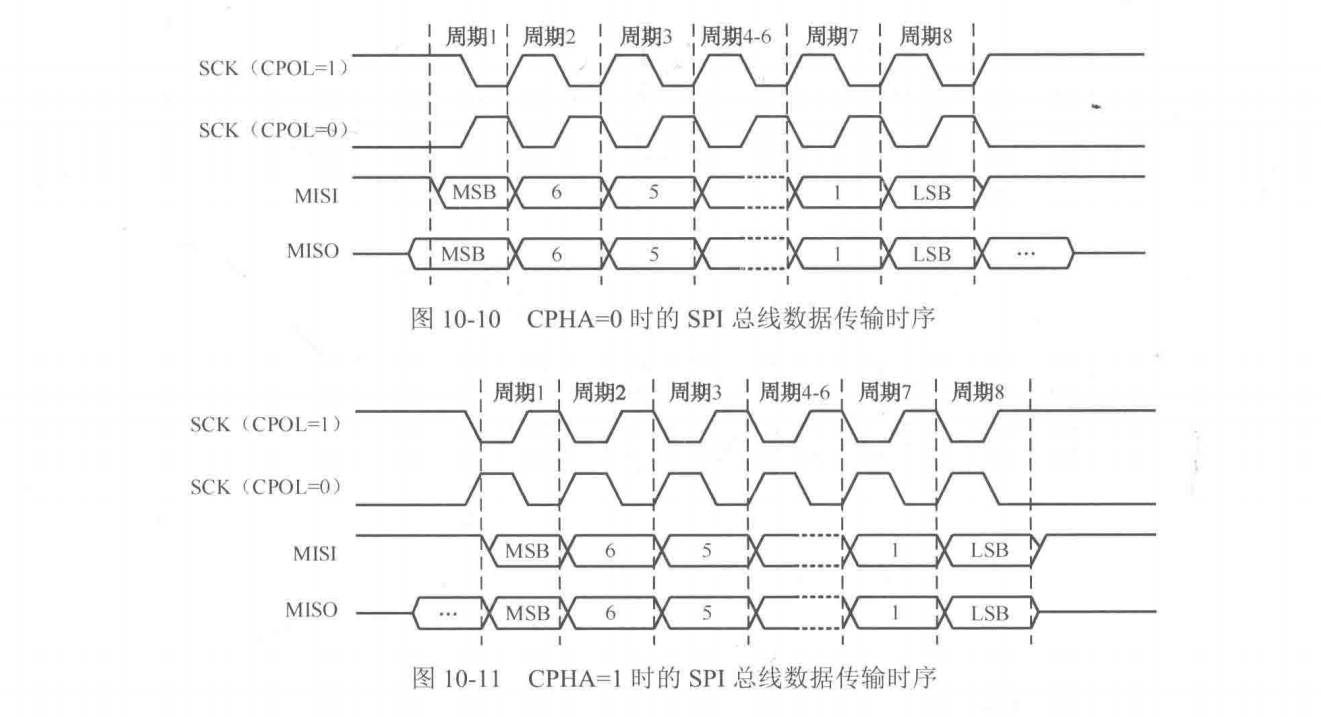

SPI模塊為了和外設進行數據交換,根據外設工作要求,其輸出串行同步時鍾極性和相位可以進行配置,SCK時鍾極性(CPOL)對傳輸協議沒有重大的影響。

如果CPOL=0,串行同步時鍾的空閑狀態為低電平;如果CPOL=1,串行同步時鍾的空閑狀態為高電平。時鍾相位(CPHA)能夠配置用於選擇兩種不同的傳輸協議之一進行數據傳輸。如果CPHA=0,在串行同步時鍾的第一個跳變沿(上升或下降)數據被采樣,SPI接口時序如圖10-10所示;如果CPHA=1,在串行同步時鍾的第二個跳變沿(上升或下降)數據被采樣,SPI接口時序如圖10-11所示。SPI主模塊及與之通信的外設時鍾相位和極性應該一致。

串行輸入A/D芯片TLC2543接口技術

TLC2543引腳分配

TLC2543是一款擁有11路模擬輸入通道,串行輸出的12位模數轉換器芯片。它采用逐次逼近技術實現A/D轉換,具有輸入通道多,可編程的輸出長度,轉換精度和轉換速度高等優點。

引腳功能如下:

- AIN0〜AIN10:模擬輸入通道。

- CS:片選,低電平有效。

- DATA INPUT:串行數據輸入,8位數據,高位在前,低位在后。最先輸入的4位數據用來選擇輸入通道,接下來的4位數據用來設定TLC2543的工作方式。

- DATA OUT:串行數據輸出,有3種長度:8位、12位、16位。默認輸出12位,數據輸出順序可以在工作方式中設定。

- I/O CLOCK:輸入/輸出同步時鍾。

- REF+:正的轉換參考電壓,一般釆用Vcc,最大的輸入電壓取決於正的參考電壓與負的參考電壓的差值。

- REF-:負的轉換參考電壓,非差分模式時,可直接接地。

- Vcc:系統電源正。

- GND:系統電源地。

接口時序

TLC2543的時序有兩種:使用片選信號CS和不使用片選信號CS。

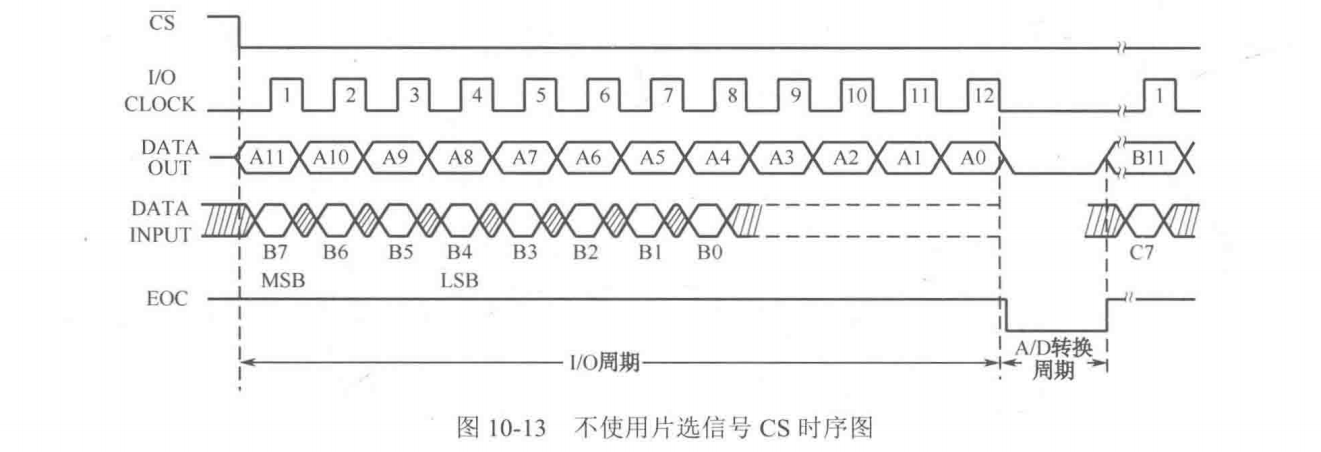

在不使用片選信號CS的情況下,只是在第一次轉換時將CS設置為低電平,以后就不再處理CS端口了,讓CS 一直處於低電平狀態。以后的每次轉換都從轉換結束信號的上升沿開始。

其時序如圖10 -13所示。

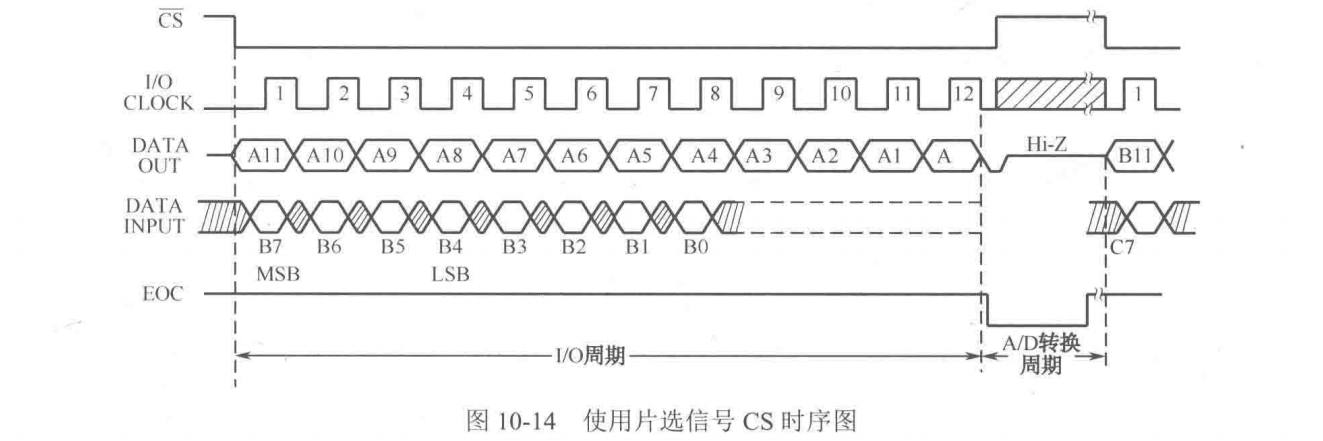

使用片選信號CS時,每次轉換都將CS變為低電平,開始寫入命令字,直到DATA OUT端移出12位數據,然后將CS變為高電平,等待轉換結束后,再將CS變為低電平,進行下一次轉換。其時序如圖10-14所示。

TLC2543輸出的數據可以是8位、12位、16位,其時序相同,它們只是在轉換周期前減少或增加4個時鍾周期。

TLC2543工作過程

TLC2543 工作過程分為兩個周期:I/O周期和實際A/D轉換周期。

TLC2543的工作由CS使能或禁止。工作時CS必須為低電平。CS被置高時,串行數據輸出端立即進入高阻態,為其他共享數據總線的器件讓出數據總線:經過一個保持時間后,I/OCLOCK、DATAINPUT被禁止。當CS再次變為低電平時,開始一個新的I/O周期。

TLC2543的工作狀態由EOC指示。復位狀態EOC總是為高,只有在I/O周期的最后一個I/O CLOCK脈沖的下降沿之后,EOC變為低電平,表示轉換周期開始。轉換完成后,轉換結果鎖入輸岀數據寄存器,EOC變高,其上升沿使轉換器返回到復位狀態,開始下一個I/O周期。

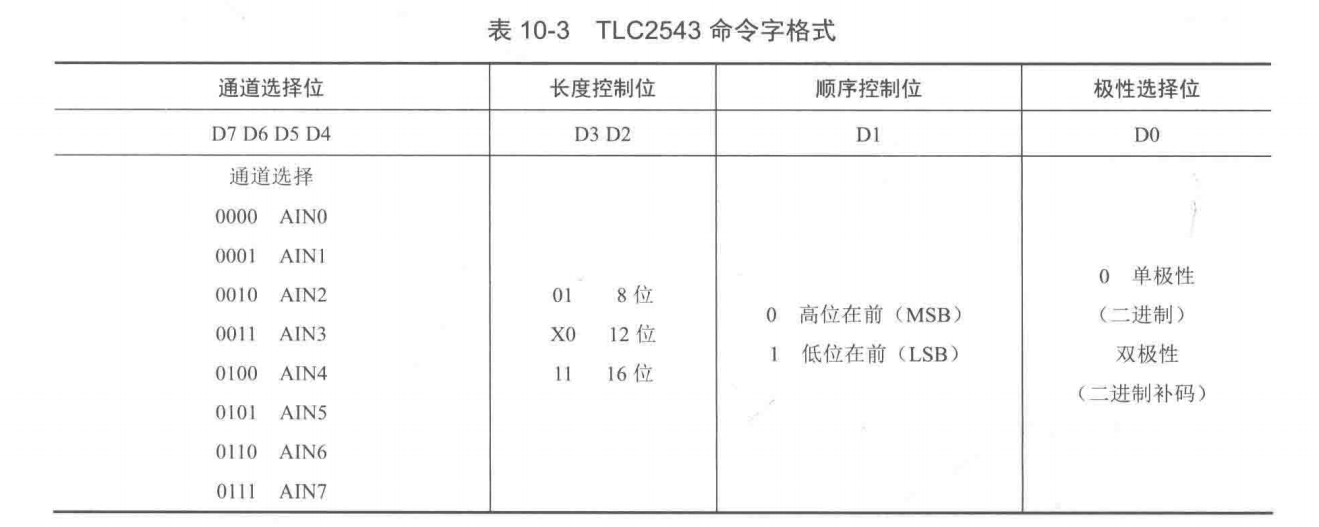

TLC2543的命令字

TLC2543每次轉換前都必須輸入一個8位命令字,包括一個4位模擬通道地址(D7〜D4)、一個2位數據長度選擇(D3〜D2)、一個輸出高位(MSB)在前或低位(LSB)在前的選擇位(D1),以及一個單極性或雙極性輸出選擇位(DO)的8位數據流。這個數據流是從DATAINPUT端加入的,命令字的輸入釆用高位在前。命令字格式如表10-3所示。

命令字通道選擇位(D7〜D4)從11個模擬通道中選擇一個進行轉換,或從3個內部自測電壓中選擇一個,以對轉換器進行校准,或者選擇軟件掉電方式。

長度控制位(D3、D2)選擇輸出數據長度:選擇12位數據長度時"所有的位都被輸出。選擇8位長度時,低4位被截取,轉換精度降低,用以實現與8位串行接口快速通信。

選擇16位時,在轉換結果的低位端增加了4個被置為0的填充位,可以方便地與16位串行接口通信。順序控制位D1選擇輸出數據的傳送方式,即下一個I/O周期數據以低位在前還是高位在前輸出數據。極性選擇位DO選擇轉換結果以單極性還是雙極性二進制數碼表示。

I2C總線串行拓展技術

I2C總線概述

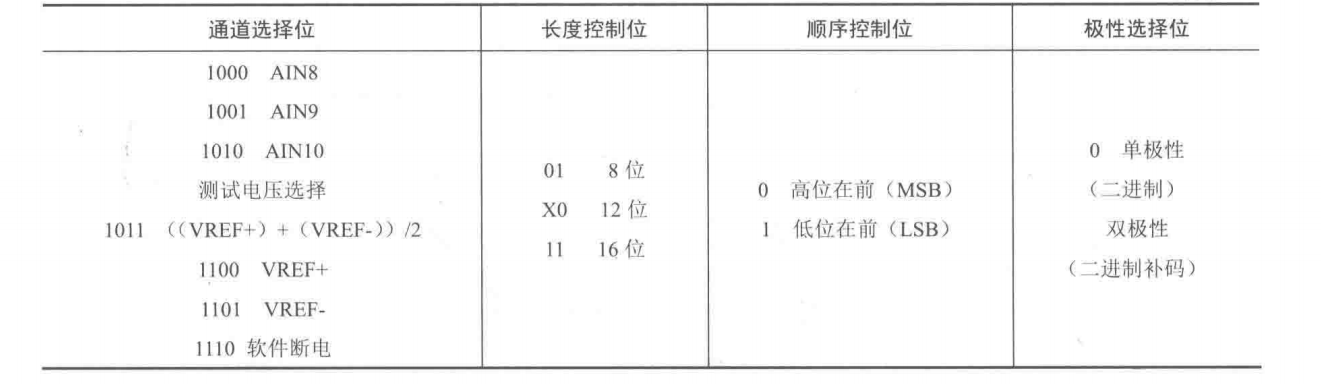

I2C是Inter-Integrated Circuit的縮寫。I2C總線是一種由Philips公司開發的串行總線,用於連接微控制器及其外圍設備。具有I2C接口的設備有微控制器、ADC、DAC、存儲器、LCD控制器、LCD驅動器以及實時時鍾等。

釆用I2C總線標准的器件,其內部不僅有I2C接口電路,而且將內部各單元電路按功能划分為若干相對獨立的模塊,通過軟件尋址實現片選,減少了器件片選線的連接。CPU不僅能通過指令將某個功能單元掛靠或脫離總線,還可對該單元的工作狀況進行檢測,從而實現對硬件系統簡單而靈活的擴展和控制。I2C只有兩條物理線路:一條串行數據線(SDA), 一條串行時鍾線(SCL)。

其連接方法如圖10-16所示。

連接到I2C總線上的設備分兩類:主控設備和從控設備。它們都可以是數據的發送器和接收器,但是數據的接收和發送的發起者只能是主控設備。正常情況下,I2C總線上的所有從控設備被設置為高阻狀態,而主控設備保持高電平,表示空閑狀態。

I2C具有如下特點:

- 只有兩條物理線路,一條串行數據線(SDA), 一條串行時鍾線(SCL);

- 每個連接到總線的器件都可以使用軟件根據它的唯一地址來識別;

- 傳輸數據的設備間是簡單的主從關系;

- 主機可以用作主機發送器或主機接收器;

- 它是一個真正的多主機總線,兩個或多個主機同時發起數據傳輸時,可以通過沖突檢測和仲裁來防止數據被損壞;

- 串行的8位雙向數據傳輸,位速率在標准模式下可達100Kbps,在快速模式下可達400Kbps,在高速模式下可達3.4Mbps。

I2C總線協議

起始條件和停止條件

I2C總線的操作模式為主從模式,即主發送模式、主接收模式、從發送模式和從接收模式。

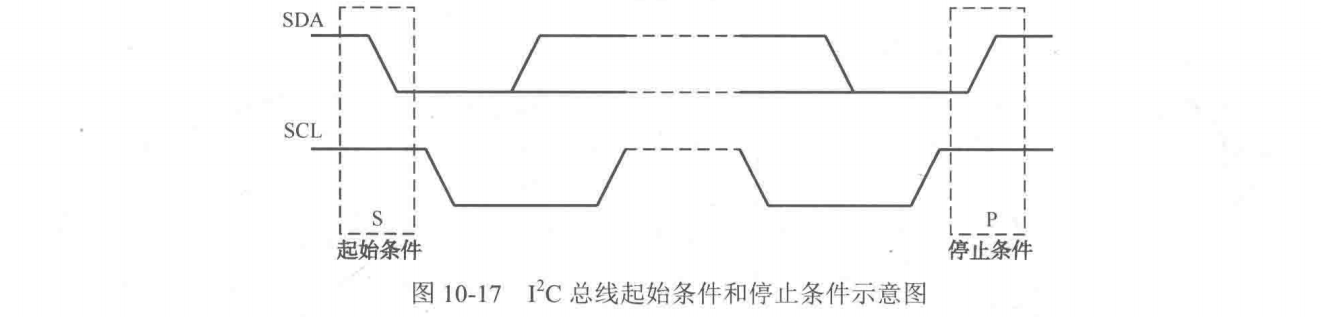

當I2C處於從模式時,若要傳輸數據,必須檢測SDA線上的起始條件,起始條件由主控設備產生。起始條件在SCL保持高電平期間,SDA由高電平向低電平的變化狀態如圖10-17所示。

當I2C總線上產生了一個起始條件時,這條總線就被發出起始條件的主控器占用了,變成“忙”狀態;而在SCL保持高電平期間,若SDA是由低電平向高電平變化狀態則規定為停止條件。

如圖10-17所示。停止條件也是由主控設備產生的,當主控器產生一個停止條件時,則停止數據傳輸,總線被釋放,I2C總線變成“閑”狀態。

從機地址

當主控器發出一個起始條件后,它還會立即送出一個從機地址,來通知與之進行通信的從器件。一般從機地址由7位地址位和1位讀/寫標志R/W組成,7位地址占據高7位,讀/寫位在最后。讀/寫位是0,表示主機將要向從機寫入數據;讀/寫位是1,則表示主機將要從從機讀取數據。

帶有I2C總線的器件除了有從機地址(Slave Address)外,還可能有子地址。從機地址是指該器件在I2C總線上被主機尋址的地址,而子地址是指該器件內部不同部件或存儲單元的編址。例如,帶I2C總線接口的E2PROM就擁有子地址。某些器件(只占少數)內部結構比較簡單,可能沒有子地址,只有必需的從機地址。與從機地址一樣,子地址實際上也是像普通數據那樣進行傳輸的,傳輸格式仍然是與數據相統一的,

區分傳輸的到底是地址還是數據要靠收發雙方具體的邏輯約定。子地址的長度必須由整數個字節組成,可能是單字節(8位子地址),也可能是雙字節(16位子地址),還可能是3字節以上,這要看具體器件的規定。

數據傳輸控制

I2C總線總是以字節(Byte)為單位收發數據,每個字節的長度都是8位,每次傳送字節的數量沒有限制。

I2C總線首先傳輸的是數據的最高位(MSB),最后傳輸的是最低位(LSB)。另外,每個字節之后還要跟一個響應位,稱為應答。接收器接收數據的情況可以通過應答位來告知發送器。應答位的時鍾脈沖仍由主機產生,而應答位的數據狀態則遵循“誰接收誰產生”的原則,即總是由接收器產生應答位。

主機向從機發送數據時,應答位由從機產生:主機從從機接收數據時,應答位由主機產生。I2C總線標准規定:應答位為“0”,表示接收器應答(ACK),簡記為A;應答位為“1”,則表示非應答(NACK),簡記為入。發送器發送完LSB之后,應當釋放SDA線,以等待接收器產生應答位。接收器在接收完最后一個字節的數據,或者不能再接收更多的數據時,應當產生非應答來通知發送器。發送器如果發現接收器產生了非應答狀態,則應當終止發送。

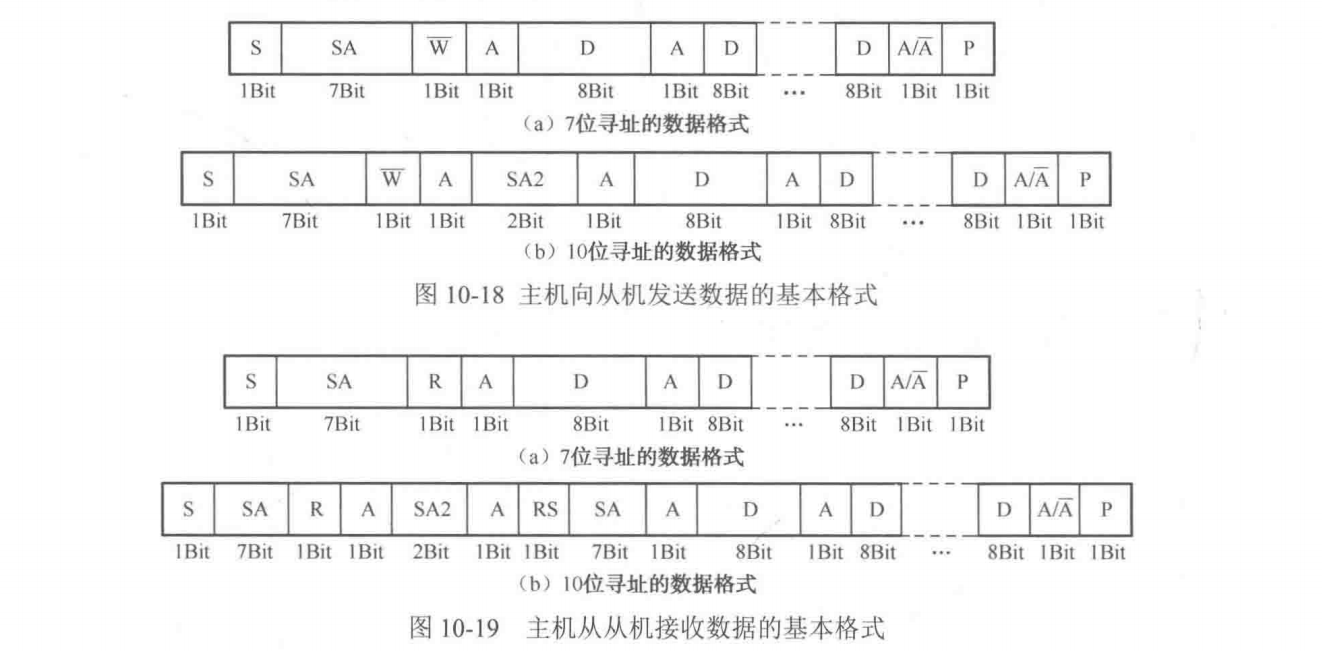

I2C總線基本數據傳輸格式根據從機地址可以分為7位尋址和10位尋址兩種數據格式,無子地址的從機地址由7位地址位和1位讀/寫位構成,稱為7位尋址方式,其數據格式如圖10-18(a)和圖10-19 (a)所示;有子地址的從機地址為10位尋址方式,分別由7位地址位、1位讀/寫位及2位子地址構成,其數據格式如圖10-18 (b)和圖10-19 (b)所示。

其中:

S:起始位(START), 1位;

RS:重復起始條件,1位;

SA:從機地址(Slave Address), 7 位;

SA2:從機子地址,2位;

W:寫標志位(Write), 1位;

R:讀標志位(Read), 1位;

A:應答位(Acknowledge), 1 位:

A :非應答位(Not Acknowledge), 1 位;

D:數據(Data),每個數據都必須是8位;

P:停止位(STOP), 1位。

數據貨輸時序圖

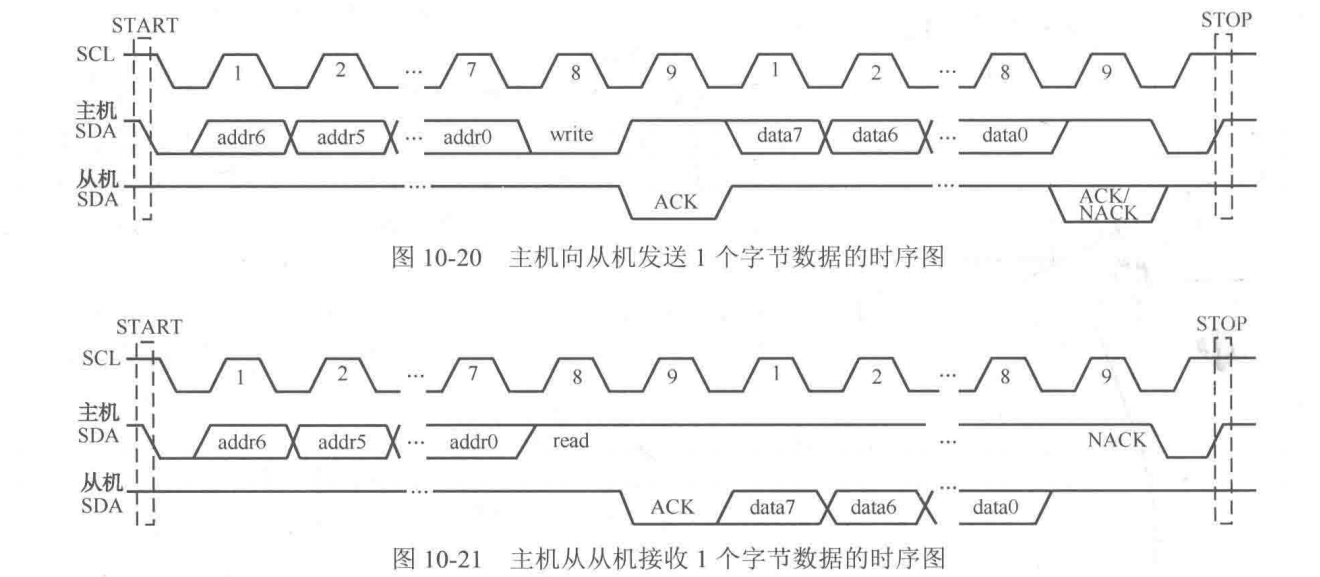

I2C總線主機向從機發送1個字節數據的時序如圖10-20所示,主機從從機接收1個字節數據的時序如圖10-21所示。

圖10-20和圖10-21中,SDA信號線被畫成了兩條,一條是主機產生的,另一條是從機產生的。實際上主機和從機的SDA信號線總是連接在一起的,是同一條SDA。畫成兩條SDA表示在I2C總線上主機和從機的不同行為。

MCS-51單片機擴展I2C總線器件的接口設計

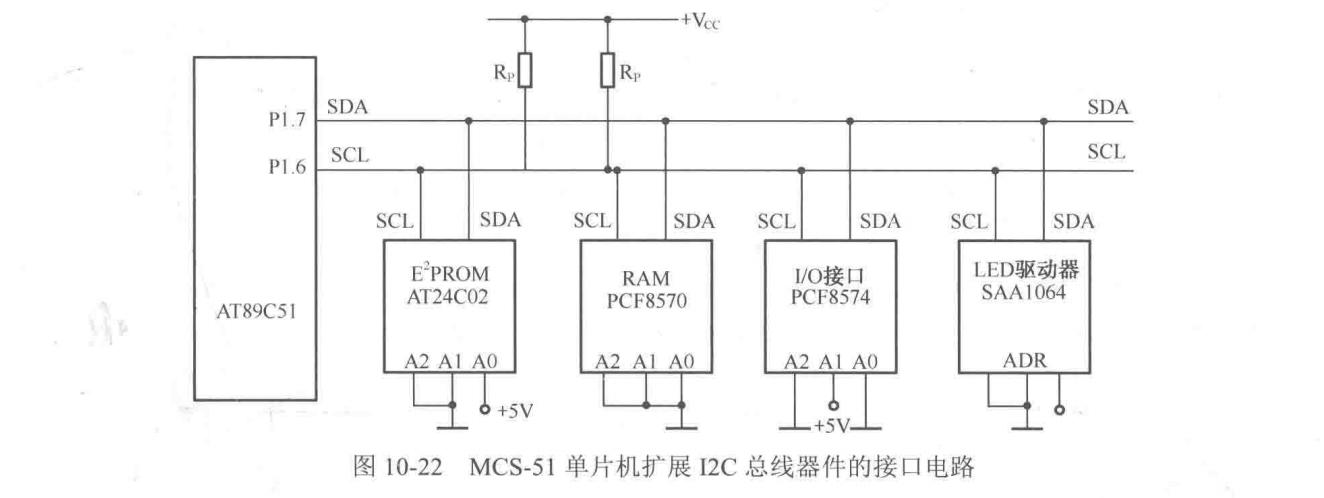

目前,許多廠商不斷推出I2C總線接口器件。對於51系列單片機,有一些品種在片上配置了I2C總線接口,但多數品種沒有配置I2C總線接口。這時可以利用通用並行I/O 口線模擬FC總線接口的時序,使這些單片機不受帶有I2C總線接口的限制。因此,在許多單片機應用系統中可以將I2C總線接口的模擬傳送技術作為常規的設計方法。

AT24C02 5草片機的接口我木

圖 10-22 中,AT24C02 為 E2PROM 芯片,PCF8570 為靜態 256x8 RAM, PCF8574 為 8位I/O 口,SAA1064為4位LED驅動器。雖然各種器件的原理和功能有很大的差異,但它們與MCS-51的連接是相同的。

Atmel公司生產的AT24CXX系列產品是I2C接口 E2PROM存儲器,串行E2PROM存儲器是各種串行接口器件中應用較多的器件。與並行的E2PROM相比,串行E2PROM的數據傳送速度較低。但是,它具有低電壓、低功耗、體積小和引腳少的特點,比較適用於速度不高、單片機I/O資源緊張的場合。

本節以AT24C02為例,簡要介紹E2PROM芯片AT24C02的引腳功能、與單片機的接口方法、信號時序和編程方法。

AT24C02引腳分配

AT24C02是一個2K位串行CMOS E2PROM,內部含有256個8位字節。AT24C02支持I2C總線數據傳送協議。數據傳送是由產生串行時鍾和所有起始停止信號的主器件控制的。主器件和從器件都可以作為發送器或接收器,但由主器件控制傳送數據(發送或接收)的模式,通過器件地址輸入端AO、A1和A2可以實現將最多8個AT24C02器件連接到總線上。

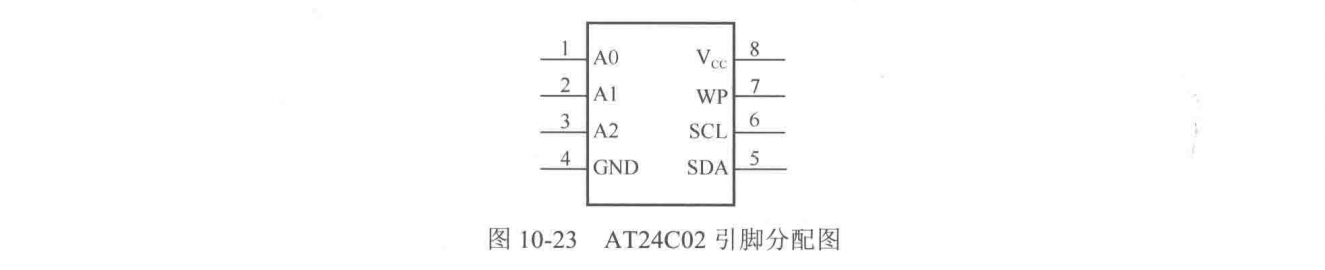

其引腳分配如圖10-23所示。

SCL:串行時鍾輸入引腳,用於產生器件所有數據發送或接收的時鍾。

SDA:串行數據/地址引腳,用於器件所有數據的發送或接收。SDA是一個開漏輸出引腳,可與其他開漏輸出或集電極開路輸出進行線或。

A0、A1、A2:器件地址輸入端,用於多個器件級聯時設置器件地址,當這些腳懸空時默認值為0。AT24C02最大可級聯8個器件,如果只有一個AT24C02被總線尋址,這3個地址輸入腳(AO、Al、A2)必須連接到GND。

WP:寫保護,如果WP引腳連接到Vcc,所有的內容都被寫保護,只能讀;當WP引腳連

接到GND或懸空,則允許器件進行正常的讀/寫操作。

AT24C02的存儲結構和尋址方式

AT24C02的存儲容量為2Kb,內容分成32頁,每頁8B,共256B。操作時有兩種尋址方式:芯片尋址和片內子地址尋址。

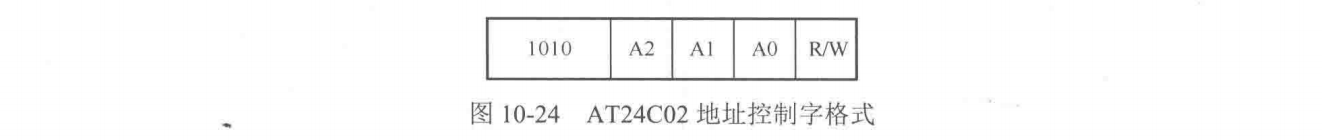

- 芯片尋址:AT24C02的芯片地址為1010,其地址控制字格式如圖10-24所示。

其中A2、Al、AO為可編程地址選擇位。A2、Al、A0引腳接高、低電平后得到確定的3位編碼,與1010形成7位編碼,即為該器件的地址碼。R/W為芯片讀/寫控制位,該位為0,表示芯片進行寫操作。

- 片內子地址尋址:芯片尋址可對內部256B中的任一個進行讀/寫操作,其尋址范圍為00〜FF,共256個尋址單位。

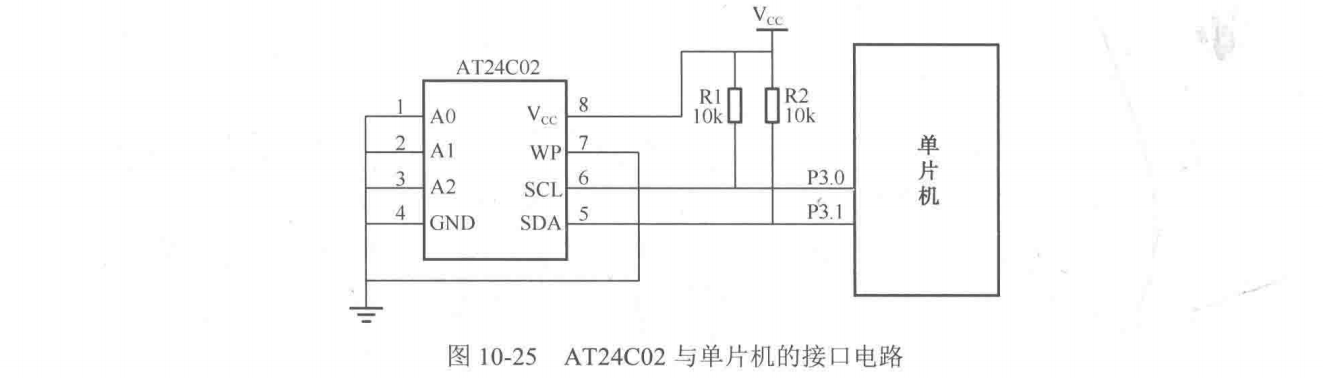

AT24C02與單片機的接口

AT24C02的SCL和SDA分別與單片機的P3.0和P3.1連接,AT24C02的A2、Al、A0、WP分別接低電平,則AT24C02的地址為A0。其連接圖如圖10-25所示。