概述

MCS-51單片機片內集成了各種存儲器和I/O功能部件,但有時根據應用系統的功能需求,片內的資源還不能滿足需要,還需要外擴存儲器和I/O功能部件(也稱I/O接口部件),這就是通常所說的MCS-51單片機的系統擴展問題。

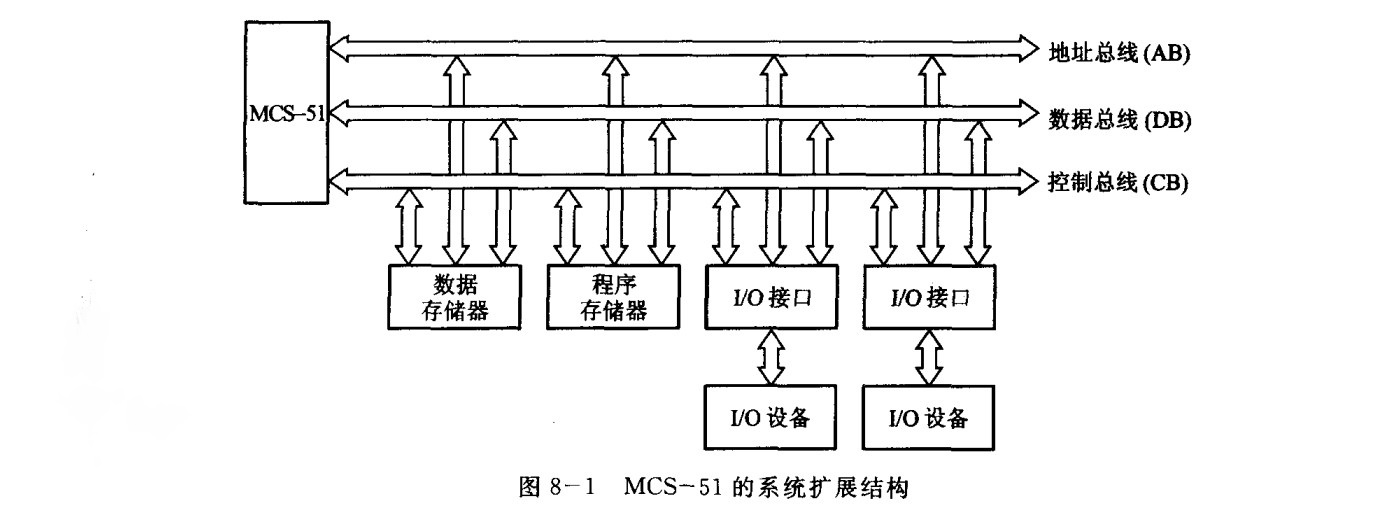

MCS-51系統擴展的內容主要有外部存儲器的擴展(外部存儲器又分為外部程序存儲器和外部數據存儲器)和I/O接口部件的擴展。本章介紹MCS-51單片機如何擴展外部存儲器,有關I/O接口部件的擴展將在下一章介紹。MCS-51系統擴展結構如圖8-1所示。

由圖8-1可以看出:系統擴展是以MCS-51單片機為核心進行的。擴展內容包括擴展程序存儲器(ROM)、數據存儲器(RAM)、I/O接口部件及I/O設備等。

MCS-51單片機外部存儲器結構,采用的是哈佛結構,即程序存儲器的空間和數據存儲器的空間是截然分開的。還有一種外部存儲器的結構,它是程序存儲器和數據存儲器合用一個空間的結構:普林斯頓結構。例如,MCS-96單片機的存儲器結構就是采用普林斯頓結構。

MCS-51單片機數據存儲器和程序存儲器的最大擴展空間各為64 KB,擴展后,系統形成了 2個並行的64 KB外部存儲器空間。

由圖8-1可以看出,擴展是通過系統總線進行的,通過總線把MCS-51單片機與各擴展部分連接起來,並進行數據、地址和控制信號的傳送。因此,要進行系統擴展首先要構造系統總線。

系統總線及總線構造

系統總線

所謂總線,就是連接計算機各部件的一組公共信號線。MCS-51使用的是並行總線結構,按其功能通常把系統總統分為三組,即:

- 地址總線(Address Bus,簡寫AB)

地址總線用於傳送單片機發出的地址信號,以便進行存儲單元和I/O端口的選擇。地址總線是單向的,只能由單片機向外送出。地址總線的數目決定着可直接訪問的存儲單元的數目。例如,”位地址,可以產生地址的數目為2”個連續地址編碼,因此可以訪問2”個存儲單元,即通常所說的尋址范圍為2”個地址單元。MCS-51單片機最多可以擴展64 KB,即65536個地址單元,因此,地址總線為16條。 - 數據總線(Data Bus,簡寫DB)

數據總線用於在單片機與存儲器之間或單片機與I/O之間傳送數據。單片機系統數據總線的位數與單片機處理數據的字長一致。MCS-51單片機是8位字長,所以,數據總線的位數也是8位的。數據總線是雙向的,可以進行2個方向的傳送。 - 控制總線(Control Bus,簡寫CB)

控制總線實際上就是一組控制信號線,包括單片機發出的,以及從其它部件傳送給單片機的。對於一條具體的控制信號線來說,其傳送方向是單向的,但是由不同方向的控制信號線組合的控制總線則表示為雙向。

由於單片機系統采用總線結構形式,可以大大減少單片機系統中傳輸線的數目,提高了系統的可靠性,增加了系統的靈活性。此外,總線結構也使擴展易於實現,各功能部件只要符合總線規范就可以很方便地接入系統,實現單片機的

系統擴展。

構造系統總線

既然單片機的擴展系統是並行總線結構,因此單片機系統擴展的首要問題就是構造系統總線,然后再往系統總線上“掛”存儲器芯片或I/O接口芯片,“掛”存儲器芯片就是存儲器擴展,“掛” I/O接口芯片就是I/O擴展。

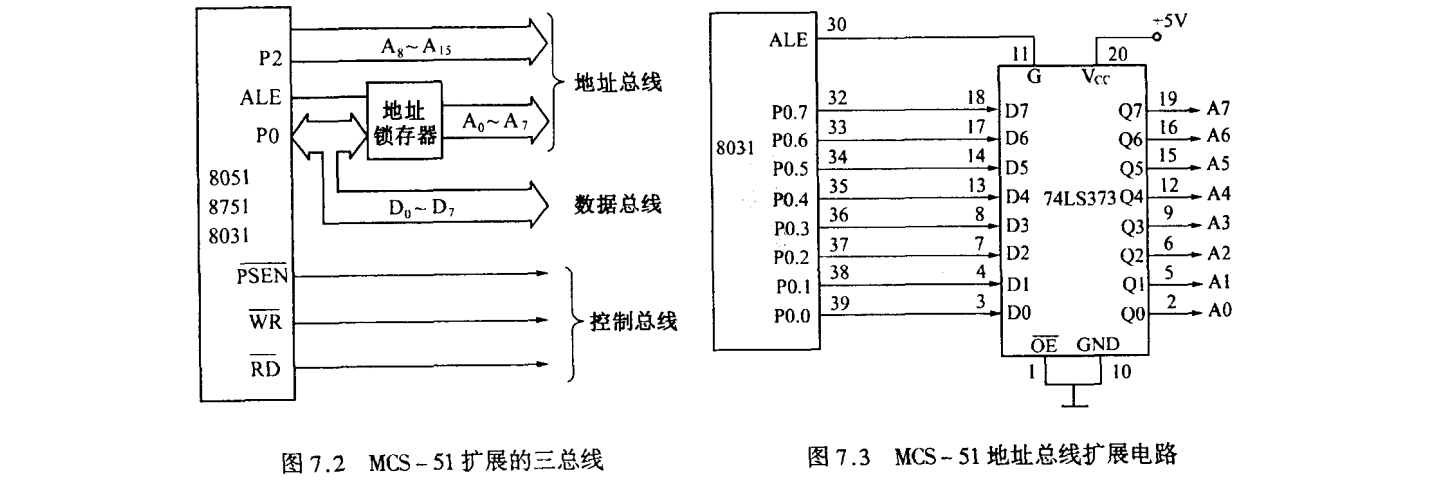

MCS-51單片機受引腳數目的限制,數據線和低8位地址線是復用的,而P0口線兼用。為了將它們分離出來,以便同單片機片外的擴展芯片正確的連接,需要在單片機外部増加地址鎖存器,從而構成與一般CPU相類似的片外三總線,如圖7.2所示。

地址鎖存器一般采用74LS373,采用74LS373的地址總線的擴展電路如圖7.3所示。

由MCS-51的P0 口送出的低8位有效地址信號是在ALE(地址鎖存允許)信號變高的同時出現的,並在ALE由高變低時,將出現在P0 口的地址信號鎖存到外部地址鎖存器74LS373中,直到下一次ALE變高時,地址才發生變化,隨后,P0 口又作為數據總線口。

下面說明總線的具體構造方法。

-

以P0 口作低8位地址/數據總線鎖存器

因為P0口即作低8位地址線,又作數據線(分時復用),因此,需要增加一個8位鎖存器。在實際應用時,先把低8位地址送鎖存器暫存,然后再由地址鎖存器給系統提供低8位地址,而把P0 口線作為數據線使用。實際上,MCS-51單片機的P0口的電路設計已考慮了這種應用要求,P0口線內部電路中的多路轉接電路MUX以及地址/數據控制就是為此目的而設計的。

-

以P2 口的口線作高位地址線

如果使用P2 口的全部8位口線,再加上P0 口提供的低8位地址,便可形成完整的16位地址總線,使單片機系統的尋址范圍達到64KB。但在實際應用系統中,高位地址線並不固定為8位,需要用幾位就從P2 口中引出幾條口線。 -

控制值號線

除了地址線和數據線之外,在擴展系統中還需要一些控制信號線,以構成擴展系統的控制總線。這些信號有的是單片機引腳的第一功能信號,有的則是第二功能信號。其中包括:- 使用ALE信號作為低8位地址的鎖存控制信號。

- 以PSEN信號作為擴展程序存儲器的讀選通信號。

- 以EA信號作為內外程序存儲器的選擇控制信號。

- 以RD和WR信號作為擴展數據存儲器和I/O 口的讀選通、寫選通信號。

可以看出,盡管MCS-51單片機有4個並行的I/O 口,共32條口線,但由於系統擴展的需要,真正作為數據I/O使用的,就剩下P1 口和P3 口的部分口線了。

單片機系統的串行擴展技術

隨着單片機技術的發展,並行總線擴展(利用3組總統AB、DB、CB進行的系統擴展)已不再是單片機唯一的系統擴展結構了,隨着集成電路芯片的集成度和結構的發展,近年來除並行總線擴展技術之外,又出現了串行總線擴展技術。

串行擴展技術具有顯著的優點,一般地說,串行接口器件體積小,因而,所占用電路板的空間,僅為並行接口器件的10%,明顯地減少了電路板空間和成本。串行接口器件與單片機接口時需要的I/O 口線很少(僅需3-4根),極大地簡化了器件之間的連接,進而提高了可靠性。

串行擴展是是通過串行接口實現的,這樣可以減少芯片的封裝引腳,降低成本,簡化了系統結構,增加系統擴展的靈活性。為了實現串行擴展,一些公司(例如PHILIPS和ATMEL公司等)已經推出了非總線型單片機芯片,並且具有SPI(Serial Periperal Interface)三線總線和PC公用雙總統的兩種申行總線形式。與此相配套,也推出了相應的串行外圍接口芯片。

但是,一般串行接口器件速度較慢,在大多數應用的場合,還是並行擴展法占主導地位。在進行系統擴展時,應對單片機的系統擴展能力、擴展總線及擴展應用特點有所了解,這樣才順利的完成系統擴展任務。

讀寫控制、地址空間分配和外部地址鎖存器

存儲器拓展的讀寫控制

外擴的RAM芯片既能讀出又能寫人,所以通常都有讀寫控制引腳,記為OE和WE。外擴RAM的讀寫控制引腳分別與MCS-51的RD和WR引腳相連。

外擴的EPROM在正常使用中只能讀出,不能寫入,故EPROM芯片沒有寫入控制引腳,只有讀出引腳,記為OE,該引腳與MCS-51單片機的歯J引腳相連。

存儲器地址空間分配

在實際的單片機應用系統設計中,既需要擴展程序存儲器,往往又需要擴展數據存儲器。

在MCS-51擴展多片的程序存儲器、數據存儲器芯片的情況下,如何把外部各自的64KB的空間分配給各個芯片,並且使程序存儲器的各個芯片之間、數據存儲器(I/O接口芯片也作為數據存儲器一部分)各芯片之間,地址不能發生重疊,以使單片機讀、寫外部存儲器時,避免發生數據沖突。這就是存儲器的地址空間的分配問題。

存儲器的地址空間分配,實際上就是使用系統提供的地址線,通過適當連接,最終達到一個存儲器單元只對應一個地址的要求。

MCS-51通過地址總線發出的地址是用來選擇某一個存儲器單元,在外擴的多片存儲器芯片中,MCS-51要完成這種功能,必須進行兩種選擇:一是必須選中該存儲器芯片(或I/O接口芯片),這稱為片選。只有被“選中”的存儲器芯片才能被MCS-51讀出或寫入數據。二是必須選擇出該芯片的某一單元,稱為單元選擇。為了芯片選擇(片選)的需要,每個存儲器芯片都有片選信號引腳,因此芯片的選擇的實質就是如何通過MCS-51的地址線來產生芯片的片選信號。

通常把單片機系統的地址籠統地分為低位和高位地址,存儲器芯片的某一存儲單元選擇使用低位地址,剩下的高位地址才作為芯片選擇使用,因此芯片的選擇都是使用高位地址線。

實際上,在16位地址線中,高、低位地址線的數目並不是固定的,我們只是把用於存儲單元選擇所使用的地址線,都稱為低位地址線,剩下多少就有多少高位地址線。存儲器地址空間分配除了考慮地址線的連接外,還討論各存儲器芯片在整個存儲空間中所占據的地址范圍,以便在程序設計時正確地使用它們。

常用的存儲器地址分配的方法有兩種:線性選擇法(簡稱線選法)和地址譯碼法(簡稱譯碼法),下面分別予以介紹。

線選法

線選法就是直接利用系統的高位地址線作為存儲器芯片(或I/O接口芯片)的片選信號。為此,只需把用到的高位地址線與存儲器芯片的片選端直接連接即可。

線選法的優點是電路簡單,不需要地址譯碼器硬件,體積小,成本低。缺點是可尋址的器件數目受到限制,故只用於不太復雜的系統中。另外,地址空間不連續,每一個存儲單元的地址不唯一,這會給程序設計帶來一些不方便。

下面通過一個具體例子,來說明線選法的具體應用。

假設某一單片機系統,需要外擴8KB的EPR0M(2片2732),4KB的RAM(2片6116),這些芯片與MCS -51單片機的接口電路如圖7.4所示,這里只畫出與地址分配有關的地址線連線。

先看程序存儲器2732與MCS-51的連接。由於2732是4KB的程序存儲器,有12根地址線A11 ~ A0,它們分別與單片機的P0口及P2.0-P2.3相連,從而實現4K字節單元的選擇(存儲單元選擇使用低位地址)。電於系統中有2片程序存儲器,存在2片程序存儲器芯片之間相區別的問題,2732(1)片選CE接A15(P2.7),2732(2)片選端赤接A14(P2.6)(片選使用高位地址),當要選中某個芯片時,單片機P2 口對應的片選信號引腳應為低電平,其它引腳一定要為高電平。這樣才能保證一次只選中一片,而不會再選中其它同類存儲器芯片,這就是所謂的線性選址法,簡稱線選法。

再來看數據存儲器與單片機的接口。數據存儲器也有2片芯片需要區別。這里用P2.5和P2.4分別作為這2片芯片的片選信號。當要選中某個芯片時,單片機P2 口對應的片選信號引腳應為低電平,其它引腳一定要為高電平。由於6116是2KB的,需要11根地址線作為存儲單元的選擇,而剩下的P2 口線(P2.4-P2.7)正好作為片選線。

從圖7.4中可以看出,程序存儲器2732的低2KB和數據存儲器6116的地址是重疊的。那么會不會MCS-51發出訪問2732某個單元的地址時,同時也會選中6116的的某個單元,這樣MCS-51就會同時選中兩個單元,從而發生數據沖突,產生錯誤呢?

這種情況,完全不用擔心,雖然兩個單元的地址是一樣的,但是MCS-51發給兩類存儲器的控制信號是不一樣的。如果訪問的是程序存儲器,則是PSEN信號有效;如果訪問的是數據存儲器,則是RD或WR信號有效。以上控制信號是由MCS-51執行訪問外部程序存儲器或訪問外部數據存儲器的指令產生,任何時刻只能執行一種指令,產生一種控制信號,所以不會產生數據沖突的問題。

通過上面的討論,可以得出一個重要的結論:MCS-51單片機外擴程序存儲器和數據存器的地址空間可以重疊,只是注意程序存儲器和程序存儲器之間,數據存儲器和數據存儲器之間,千萬不要發生地址重疊。現在再來看兩個程序存儲器的地址范圍。

現在再來看兩個程序存儲器的地址范圍。

2732(1)的地址范圍:

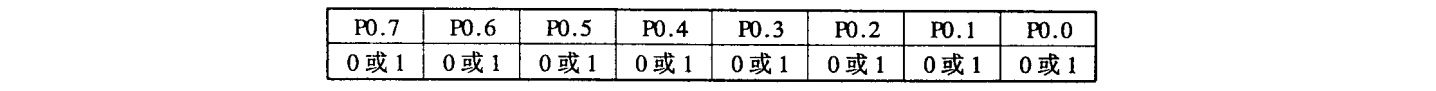

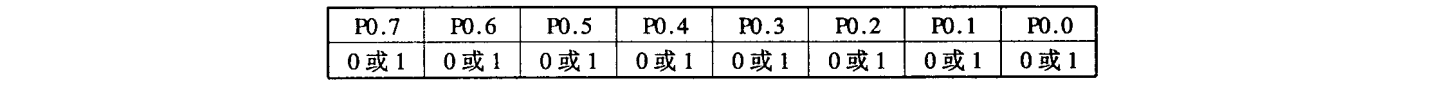

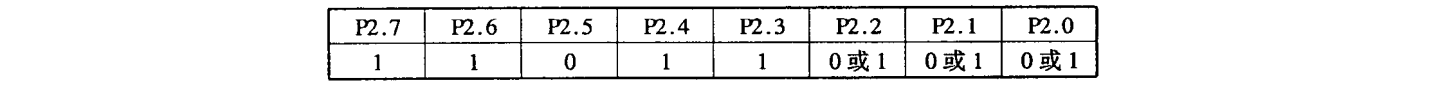

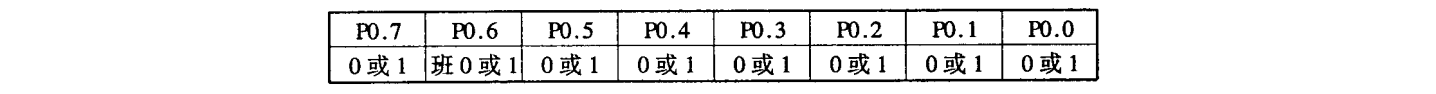

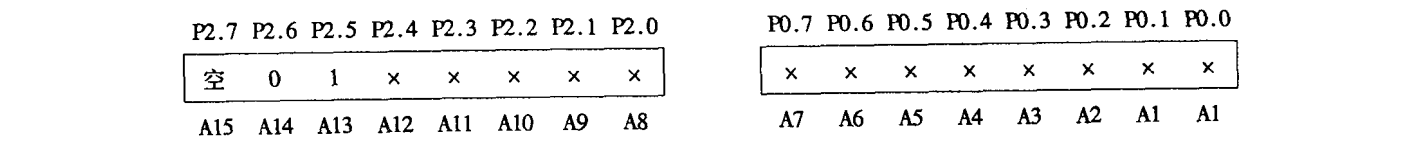

選中2732(1)時,P2 口(高8位的地址)各引腳的狀態為:

由上面介紹可見高8位的地址變化范圍:70H ~ 7FH

由上可見低8位的地址變化范圍:00H ~ FFH

所以2732(1)的地址范圍變化范圍為:7000H~7FFFH

2732(2)的地址范圍:

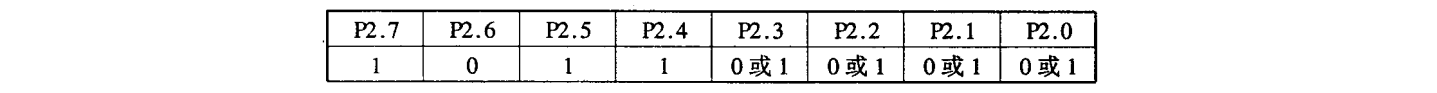

選中2732(2)時,P2 口(高8位的地址)各引腳的狀態為

由上可見高8位的地址變化范圍:BOH-BFH

由上可見低8位的地址變化范圍:00H~ FFH

所以2732(2)的地址的變化范圍為:B000H- BFFFH

現在再來看兩個數據存儲器的地址范圍。

6116(1)的地址范圍:

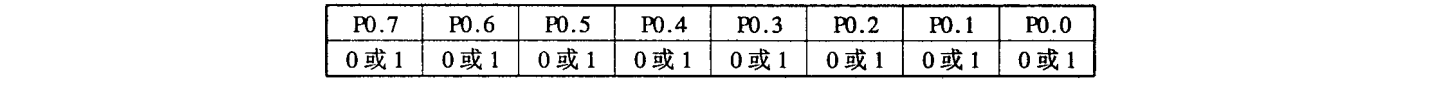

選中6116(1)時,P2 口(高8位的地址)各引腳的狀態為:

由上可見高8位的地址變化范圍:ECH ~ EFH

由上可見低8位的地址變化范圍:00H ~ FFH

所以6116(1)的地址范圍變化范圍為:EC00H~EFFFH

6116(2)的地址范圍:

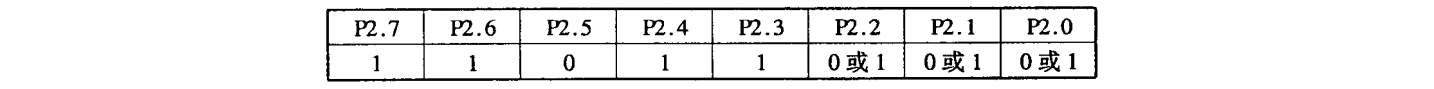

選中6116(2)時,P2 口(高8位的地址)各引腳的狀態為:

由上可見高8位的地址變化范圍:D8H~ DFH

由上可見低8位的地址變化范圍:00H~FFH

所以6116(2)的地址范圍變化范圍為:D800H-DEFFH

由上面介紹可見,線選法的特點是簡單明了,不需要另外增加硬件電路。但是,這種方法對存儲器空間的利用是斷續的,不能充分有效地利用存儲空間,擴展的存儲器容量有限,只適用於外擴的芯片數目不多,規模不大的單片機系統的存儲器擴展。

譯碼法

譯碼法就是使用譯碼器對MCS-51的高位地址進行譯碼,譯碼器的譯碼輸出作為存儲器芯片的片選信號。這是一種最常用的存儲器地址分配的方法,它能有效的利用存儲器空間,適用於大容量多芯片的存儲器擴展。

譯碼電路可以使用現成的譯碼器芯片。最常用的譯碼器芯片有:74LS138(3- 8譯碼器)7415139(雙2-4譯碼器)7415154(4- 16譯碼器),它們的CMOS芯片分別為:74HC138、74HC139、74HC154。它們使用靈活,完全可根據設計者的要求來組合譯碼,產生片選信號。

若全部地址都參加譯碼,稱為全譯碼;若部分地址參加譯碼,稱為部分譯碼,部分譯碼存在着部分存儲器地址空間相重疊的情況。

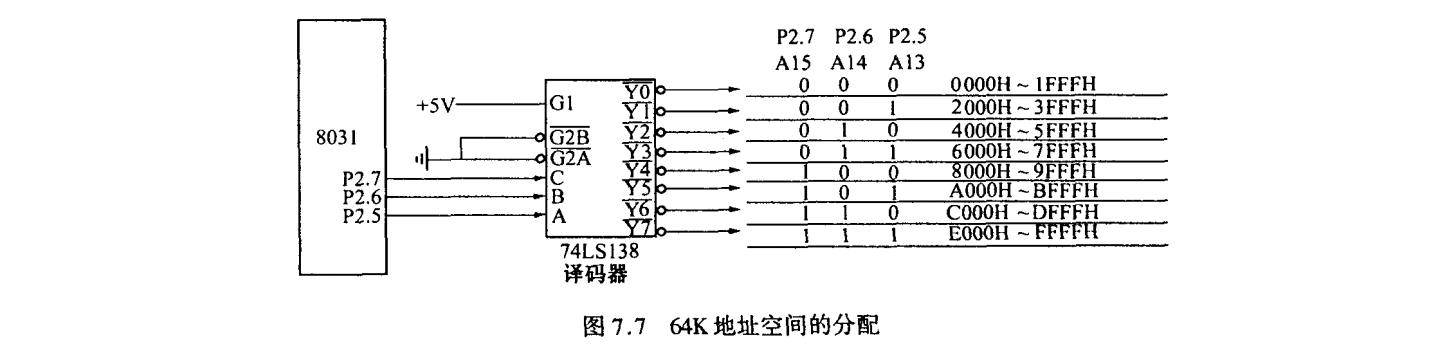

下面我們以7415138為例。來介紹如何進行地址分配。例如要擴8片8KB的RAM 6264,如何通過74LS138把64K空間分配給各個芯片?

由7415138真值表可知,把G1接到+ 5V,G2A,G2B接地,P2.7、P2.6、P2.5 分別接到 74LS138 的 C、B、A 端,P2.4 ~ P2.0,P0.7 ~ P0.0 這13根地址線接到8片6264的A12 - A0腳。

由於對高3位地址譯碼,這樣譯碼器有8個輸出Y0 ~ Y7,分別接到8片6264的片選端,而低13位地址(P2.4~ P2.0.P0.7 ~ P0.0)完成對6264存儲單元的選擇。這樣就把64K存儲器空間分成8個8K空間了。64K地址空間的分配如圖7.7所示。

這種除了單元選擇的地址線外,剰余的高位地址線全部參加譯碼的方式稱為全地址譯碼方式。由於采用的是全地址譯碼方式,MCS-51單片機發地址碼時,每次只能唯一地選中一個存儲單元。這樣,同類存儲器之間根本不會產生地址重疊的問題。

如果用74LS138把64K空間全部划分為每塊4KB,如何划分呢?由於4KB空間需要12根地址線進行單元選擇,而譯碼器的輸入有3根地址線(P2.6~P2.4),P2.7沒有參加譯碼,P2.7發出的0或1決定了選擇64KB存儲器空間的前32K還是后32K,由於P2.7沒有參加譯碼(高位地址沒有全部參加譯碼,就不是全譯碼方式),這樣,前后兩個32K空間就重疊了。

但是在實際的應用設計時,32KB存儲器空間在大部分情況下是夠用的。那么,這32KB空間利用74LS138譯碼器可划分為8個4KB空間。如果把P2.7通過一個非門與74LS138譯碼器的G1端連接起來,如圖7.8所示,這樣就不會發生兩個32K空間重疊的問題了。這時,選中的是64K空間的前32K空間,地址范圍為0000H ~ 7FFFH。如果去掉圖7.8中的非門,地址范圍為8000H ~ FFFFH。把譯碼器的輸出連到各個4K存儲器的片選端,這樣就把32K的空間划分為8個4K空間。P2.3 ~ P2.0.P0.7 ~ P0.0實現對單元的選擇,P2.6 ~ P2.4通過74LS138譯碼器的譯碼實現對存儲器的片選。

如果利用741S138譯碼器實現每塊為2KB的划分,這晚產生4個16K存儲器空間的划分。如果把P2.7同74IS138譯碼器的G1端相連,P2.6同G2A端相連,這樣一來就把64K空間固定為4個16K空間中的一個。改變P2.7.P2.6同譯碼器G1端、G2A端連接的邏輯,即可改變選中4個16K空間中的某一個。譯碼器的8個輸出,即把16KB空間划分為2KB 一個的存儲空間了。讀者可自己畫出這部分電路以及譯碼器輸出的對應地址范圍。

外部地址鎖存器

MCS-51單片機受引腳數的限制,數據線和地址線是復用的,由P0口線兼用。為了將它們分離出來,以便同單片機片外的擴展芯片正確的連接,需要在單片機外部増加地址鎖存器。目前,常用的地址鎖存器芯片有:74LS373、8282、74I&73等。

程序存儲器EPROM拓展

程序存儲器一般采用只讀存儲器,因為這種存儲器在電源關斷后,仍能保存程序(我們稱此特性為非易失性的),在系統上電后,CPU可取出這些指令予以重新執行。只讀存儲器簡稱為ROM(Read Only Memory)。ROM中的信息一旦寫入之后,就不能隨意更改,特別是不能在程序運行的過程中寫入新的內容,故稱之為只讀存儲器。

向ROM中寫入信息叫做ROM編程。根據編程的方式不同,ROM分為以下幾種:

- 掩膜ROM

掩膜ROM是在制造過程中編程。因編程是以掩膜工藝實現的,因此稱為掩膜ROM。這種芯片存儲結構簡單,集成度高,但由於掩膜工藝由於成本較高,因此只適合於大批量生產。在批量大的生產中,一次性掩膜生產成本才是很低的。 - 可編程 ROM(PROM)

PROM(可編程只讀存儲器)芯片出廠是並沒有任何程序信息,是由用戶用獨立的編程器寫入的。但PROM只能寫入一次,寫入內容后,就不能再進行修改。 - EPROM

EPROM是用電信號編程,用紫外線擦除的只讀存儲器芯片。在芯片外殼上的中間位置有一個圓形窗口,通過這個窗口照射紫外線射就可擦除原有的信息。 - E2PROM( EEPROM)

這是一種用電信號編程,也用電信號擦除的ROM芯片,對E2PROM的讀寫操作與RAM存儲器幾乎沒有什么差別,只是寫入的速度慢一些。但斷電后能夠保存信息。 - Flash ROM

Flash ROM又稱閃爍存儲器,或稱快擦寫ROMo Flash ROM是在EPROM、E2PROM的基礎上發展起來的一種只讀存儲器。是一種非易失性、電擦除型存儲器。其特點是可快速在線修改其存儲單元中的數據,標准改寫次數可達1萬次,而成本卻比普通e2prom低得多,因而可大量替代E2PROM。與E2PROM相比,E2PROM的寫入的速度較慢。但是,Flash ROM的讀寫速度都很快,存取時間可達70ns。由於其性能比E2PROM要好,所以目前大有取代E2PROM的趨勢。

EPROM芯片介紹

程序存儲器的擴展可根據需要來使用上述的各種只讀存儲器的芯片,但使用比較多的是EPROM E2PROM,下面首先對常用的EPROM芯片進行介紹。

EPROM 的典型芯片是 27 系列產品,例如,2716(2KB x 8)、2732(4KB x 8)、2764(8KB x 8)、27128( 16KB x8)、27256(32KB x 8)、27512(64KB x 8)。型號名稱“27”后面的數字表示其位存容量。如果換算成字節容量,只需將該數字除以8即可。

隨着大規模集成電路技術的發展,大容量存儲器芯片的產暈劇増,售價不斷下降。大容量存儲器芯片的性價比明顯增高,而且由於有些廠家已停止生產小容量的芯片,使市場上某些小容量芯片的價格反而比大容量芯片還貴(例如,目前2716.2732已經停止生產,在市場上已經很難買到)。所以,在擴展程序存儲器設計時,應盡量采用大容量的芯片。這樣,不僅可以使電路板的體積縮小,成本降低,還可以降低整機功耗和減少控制邏輯電路,從而提高系統的穩定性和可靠性。

常用的EPRW芯片

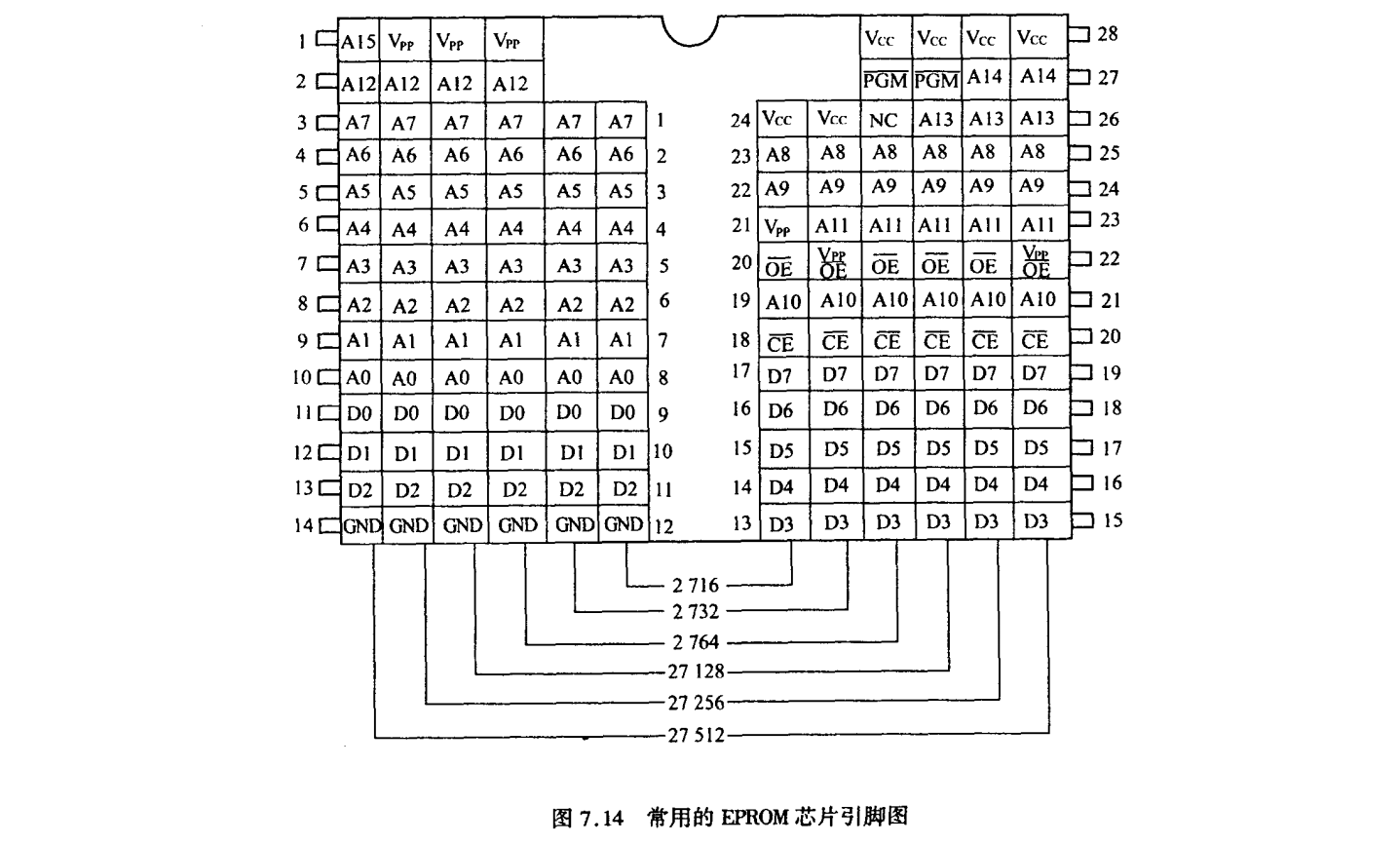

27系列EPROM的芯片的引腳如圖7.14所示。

在圖7.14中的芯片的引腳功能如下:

A15 ~ A0:地址線引腳。地址線引腳的數目由芯片的存儲容量來定,用來進行單元選擇。

D7~D0:數據引腳

CE:片選輸入端

OE:輸出允許控制端

PGM:編程時,加編程脈沖的輸入端

Vpp:編程時,編程電壓(+ 12V或+ 25V)輸入端

Vcc:+5V,芯片的工作電壓。

GND:數字地。

NC:無用端

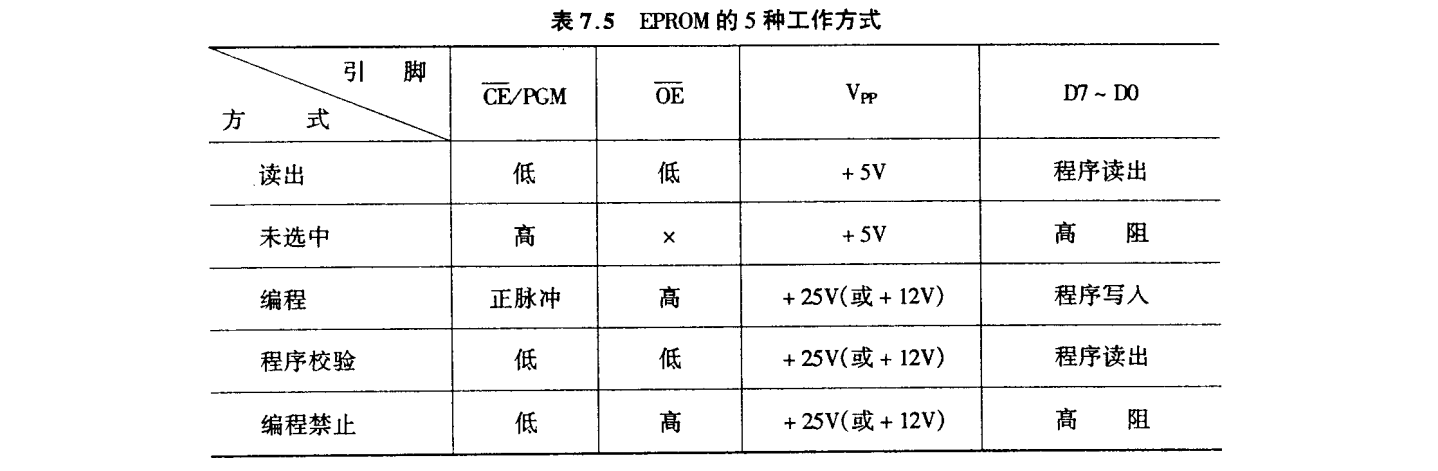

EPROM芯片的工作方式

EPROM 一般都有5種工作方式,由CE、OE、PGM各信號的狀態組合來確定。5種工作方式如表7.5所示。

- 讀出方式

一般情況下,EPROM工作在這種方式。工作在此種方式的條件是使片選控制線CE為低,同時讓輸出允許控制線OE為低,Vpp為+ 5V,就可將EPROM中的指定地址單元的內容從數據引腳D7~D0上讀出。 - 未選中方式

當片選控制線CE為高電平時,芯片進入未選中方式,這時數據輸出為高阻抗懸浮狀態,不占用數據總線。EPROM處於低功耗的維持狀態。 - 編程方式

在Vpp端加上規定好的高壓,CE和OE加上合適的電平(不同的芯片要求不同),就能將數據線上的數據寫入到指定的地址單元。此時,編程地址和編程數據分別由系統的A15-A0和D7-D0提供。 - 編程校驗方式

在Vpp端保持相應的編程電壓(高壓),再按讀出方式操作,讀出編程固化好的內容,以校驗寫入的內容是否正確。 - 編程禁止方式

本工作方式輸出呈高阻狀態,不寫入程序。

程序存儲器的操作時序

訪問程序存儲器的控制信號

MCS-51單片機訪問片外程序存儲器時,所用的控制信號有:

- ALE——用於低8位地址鎖存控制。

- PSEN——片外程序存儲器“讀選通”控制信號。PSEN接外擴EPROM的OE引腳。

- EA——片內、片外程序存儲器訪問的控制信號。EA=1時,訪問片內程序存儲器;當EA=0時,訪問片外程序存儲器。

如果指令是從片外EPROM中讀取的,除了ALE用於低8位地址鎖存信號之外,控制信號還有PSEN,PSEN接外擴EPROM的OE腳。此外,還要用到P0口和P2 口,P0口分時用作低8位地址總線和數據總線,P2 口用作高8位地址線。相應的時序圖如圖7.15所示。

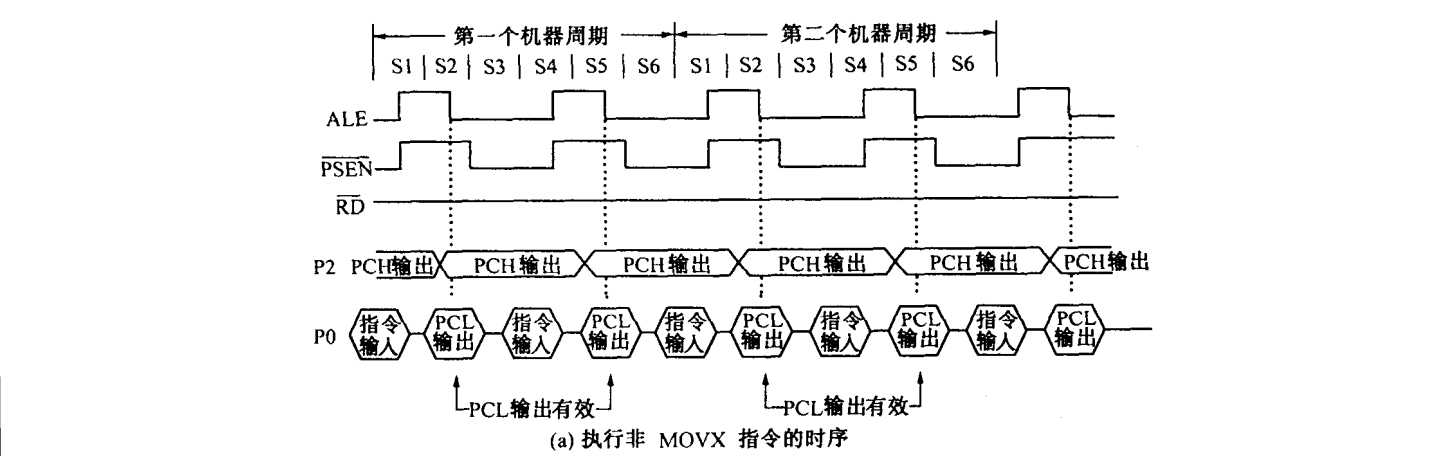

操作時序

由於MCS-51單片機中ROM和RAM是嚴格分開的,因此,對片外ROM的操作時序分為兩種情況:執行非MOVX指令的時序,如圖7.15(a)所示;執行MOVX指令的時序,如圖7.15(b)所示。

-

應用系統中無片外RAM

無片外RAM,則不用執行MOVX指令。在執行非MOVX指令時,P0 口作為地址/數據復用的雙向總線,用於輸入指令或輸出程序存儲器的低8位地址PCL。P2 口專門用於輸出程序存儲器的高8位地址PCH。

P2 口具有輸出鎖存功能;而P0 口輸出地址外,還要輸入指令,故要用ALE來鎖存P0 口輸岀的地址PCL。在每個機器周期中,允許地址鎖存信號ALE兩次有效,在ALE下降沿時,鎖存出現在P0 口上的低8位地址PCL。同時,PSEN也是每個機器周期中兩次有效,用於選通片外程序存儲器,將指令讀入片內。

系統無片外RAM時,此ALE有效信號以振盪器頻率的1/6出現在引腳上,它可以用作外部時鍾或定時脈沖信號。

-

應用系統中接有片外RAM

在執行訪問片外RAM的MOVX指令時,程序存儲器的操作時序有所變化。

其主要原因在於,執行MOVX指令時,16位地址應轉而指向數據存儲器,操作時序如圖7.15(b)所示。在指令輸入以前,P2 口、P0 口輸出的地址PCH、PCL指向程序存儲器;在指令輸入並判定是MOVX指令后,ALE在該機器周期S5狀態鎖存的P0 口的地址不是程序存儲器的低8位,而是數據存儲器的地址。

若執行的是“MOVX A,@DPTR”或“MOVX @DPTR,A”指令,則此地址就是DPL(數據指針的低8位);同時,在P2 口上出現的是DPH(數據指針的高8位)。若執行的是“MOVX A,@Ri”或“MOVX @Ri,A”指令,則Ri的內容為低8位地址,而P2 口線上將是P2 口鎖存器的內容。在同一機器周期中將不再出現PSEN有效取指信號,下一個機器周期中ALE的有效鎖存信號也不復岀現;而RD/WR有效時,P0 口將讀/寫數據存儲器中的數據。

由圖7.15(b)可以看出:

- 將ALE用作定時脈沖輸出時,執行一次MOVX指令會丟失一個脈沖。

- 只有在執行MOVX指令時的第二個機器周期期間,地址總線才由數據存儲器使用。

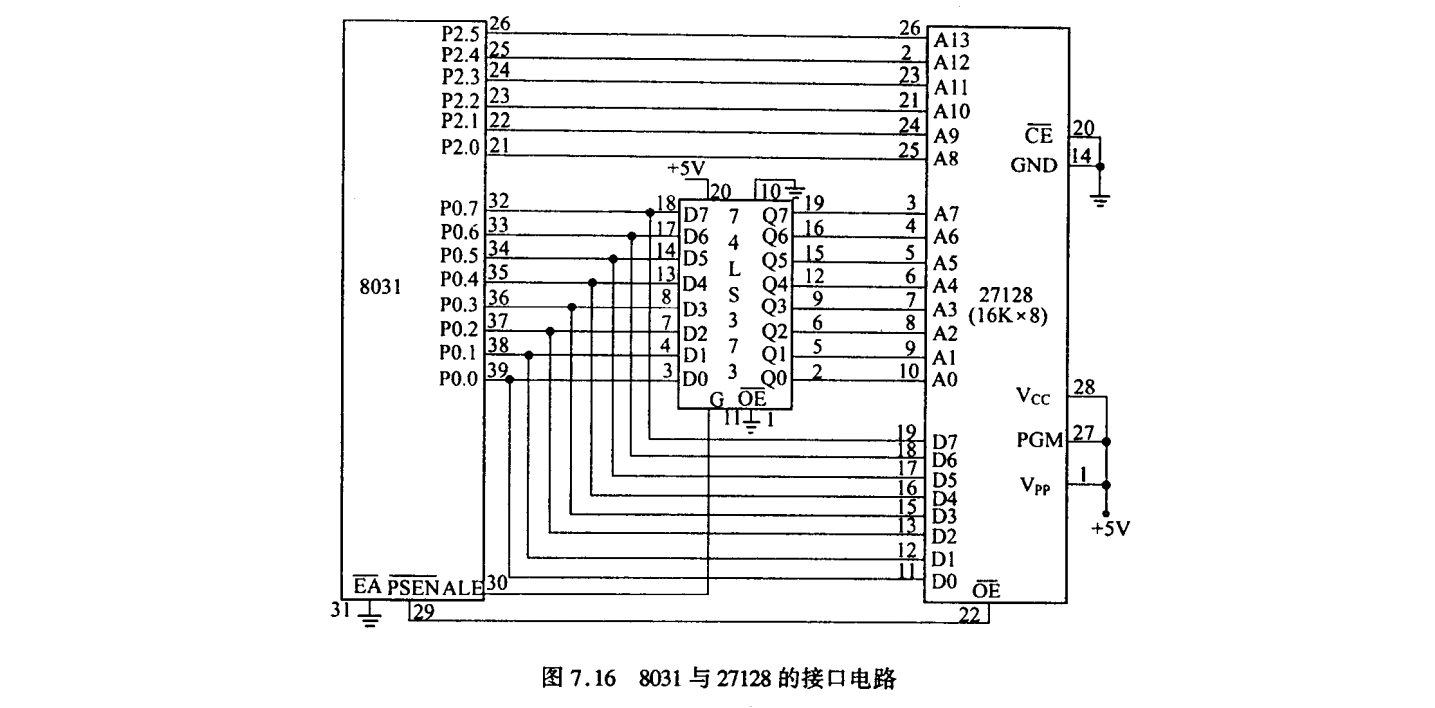

典型的EPROM接口電路

使用單片EPROM的擴展電路

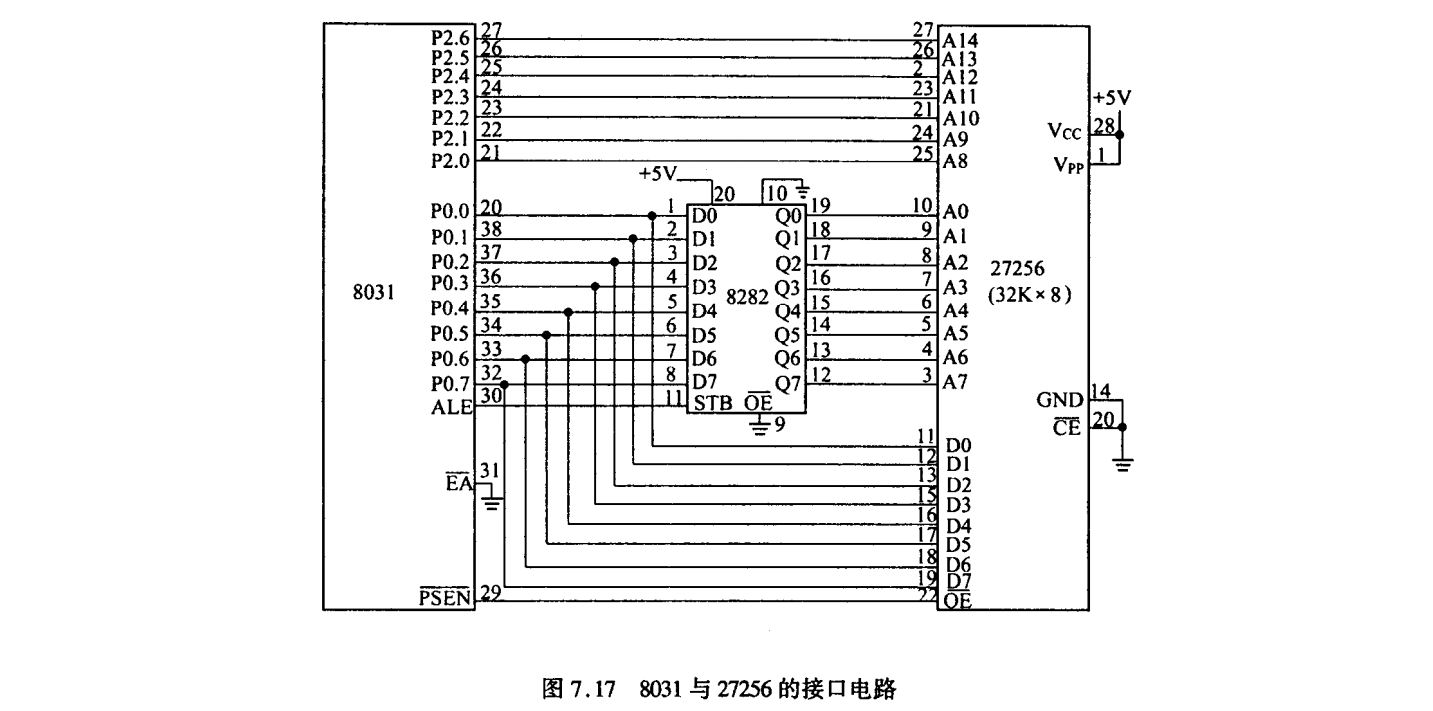

由於2764與27128引腳的差別僅在26腳上,2764的26腳是空腳,27128的26腳是地址線A13,因此在設計外擴存儲器電路時,應選用27128芯片設計電路。在實際應用時,可將27128換成2764,系統仍能正常運行,反之,則不然。圖7.16給出了 MCS-51外擴16K字節EPROM的27128的電路圖。圖7.17給岀了 MCS-51外擴32K字節的EPROM 27256的線路圖。

注意在圖7.16、圖7.17中的兩種地址鎖存器的用法。

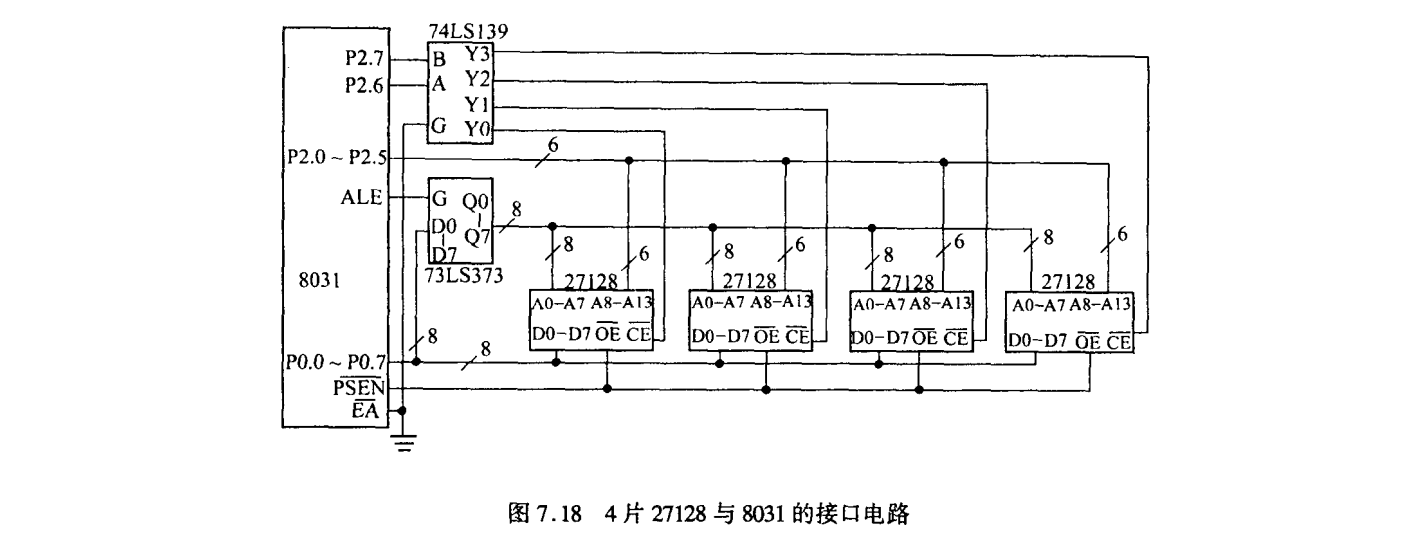

使用多片EPROM的擴展電路

與單片EPROM擴展電路相比,多片EPROM的擴展除片選線CE外,其他均與單片擴展電路相同。圖7.18給出了利用4片27128EPROM擴展成64K字節程序存儲器的方法。片選信號由譯碼選通法產生。4片27128各自所占的地址空間,請讀者自己分析。

靜態數據存儲器的拓展

MCS-51單片機內部有128個字節RAM。在實際應用中,僅靠片內RAM往往不夠用,必須擴展外部數據存儲器。常用的數據存儲器有靜態存儲器(SRAM)和動態存儲器(DRAM),在單片機應用系統中,外擴的數據存儲器都采用靜態數據存儲器。

所擴展的數據存儲器空間地址,由P2 口提供高8位地址,P0 口分時提供8位地址地址和用作8位的雙向數據總線。片外數據存儲器RAM的讀和寫由8031的RD(P3.7)和WR(P3.6)信號控制,而片外程序存儲器EPROM的輸出允許端(OE)由PSEN信號控制。盡管與E-PROM共處同一地址空間,但由於控制信號不同,故不會發生總線沖突。

常用的靜態RAM(SRAM)芯片

單片機系統中常用的SRAM芯片的典型型號有:6116(2K x 8),6264 ( 8K x 8),62128( 16K x 8) ,62256(32K x 8)。它們都用單一+5V電源供電,雙列直插封裝,6116為24引腳封裝,6264、62128、62256為28引腳封裝。

SRAM的各引腳功能如下:

A0-A14:地址輸入線。

D0~D7:雙向三態數據線。

CE:片選信號輸入線,低電平有效。對玉6264芯片,當26腳(CS)為高電平時,且衣為低電平時才選中該片。

OE:讀選通信號輸入線,低電平有效。

WE:寫允許信號輸入線,低電平有效。

Vcc:工作電源+5 Vo

GND:地線。

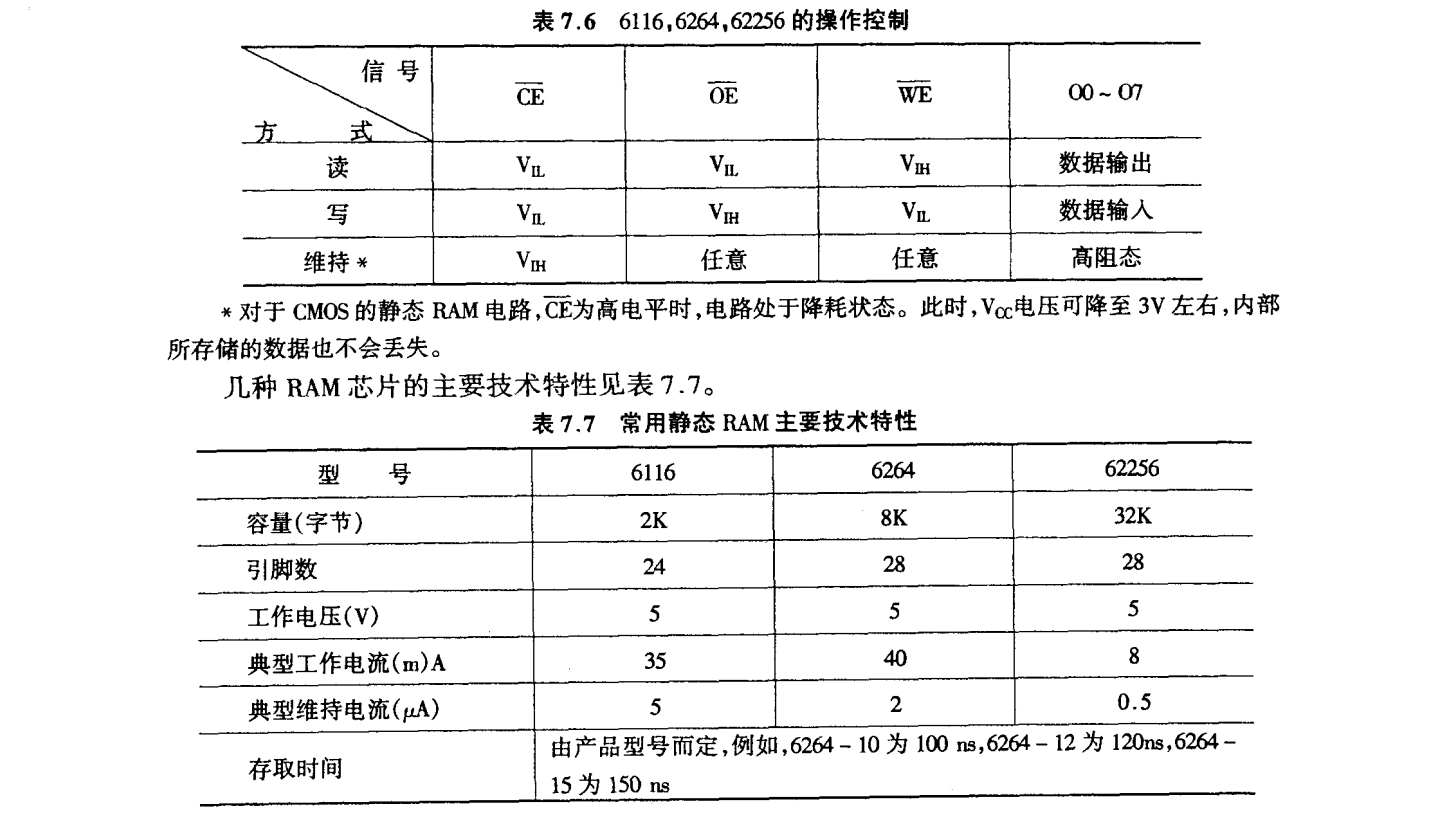

靜態RAM存儲器有讀出、寫入、維持三種工作方式,這些工作方式的操作控制如表7.6所示。

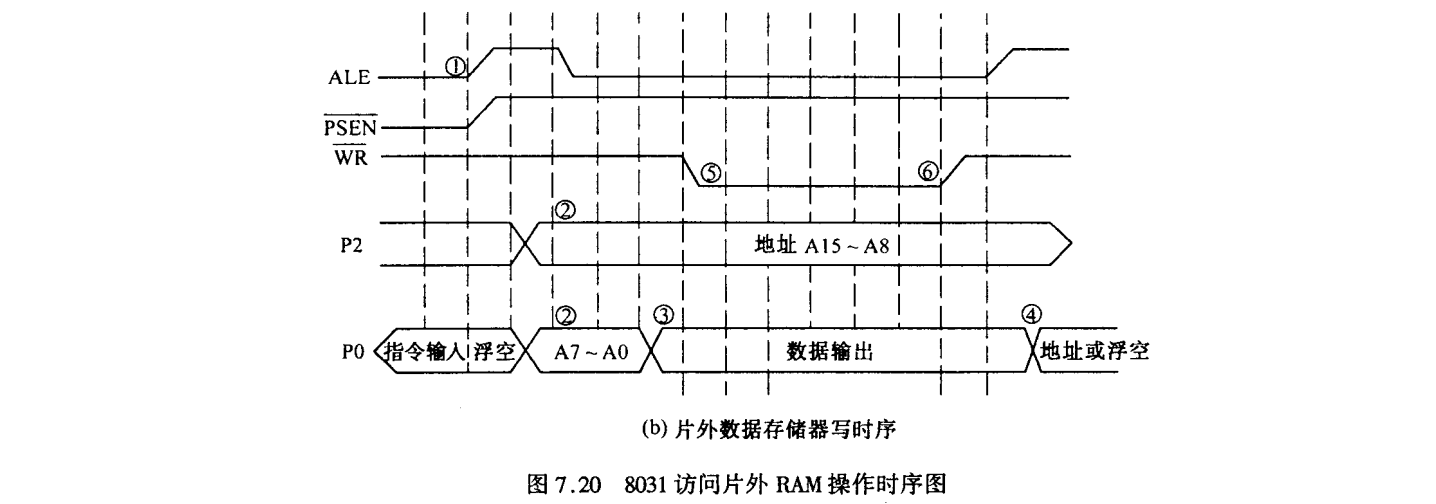

外擴數據存儲器的讀寫操作時序

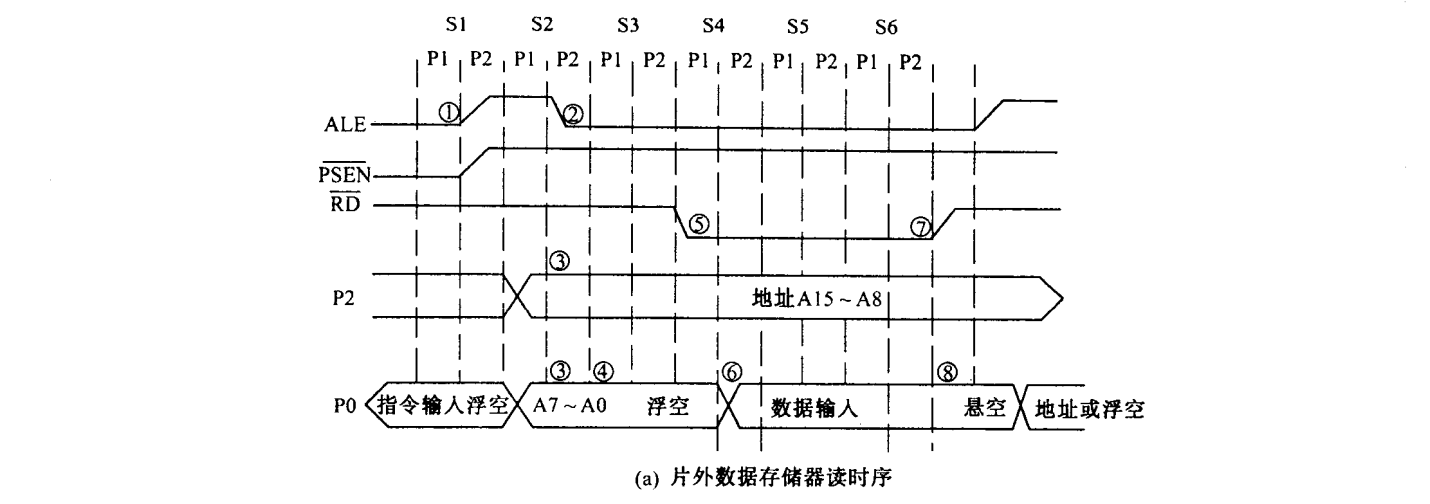

NTCS-51對外擴RAM讀和寫兩種操作時序的基本過程是相同的。所用的控制信號有ALE、RD(讀)和WR(寫)。

讀片外RAM操作時序

8031單片機若外擴一片RAM,應將其WR引腳與RAM芯片的WE引腳連接,而引腳與芯片況引腳連接。ALE信號的作用與8031外擴EPROM作用相同,即鎖存低8位地址。讀片外RAM周期時序如圖7.20(a)所示。

在第一個機器周期的S1狀態,ALE信號由低變高①,讀RAM周期開始。在S2狀態,CPU把低8位地址送到P0 口總線上,把高8位地址送上P2 口 (在執行“MOVX A, @DPTR”指令階段時才送高8位;若是“MOVX A, @Ri”則不送高8位)。

ALE的下降沿②用來把低8位地址信息鎖存到外部鎖存器74LS373內③。而高8位地址信息一直鎖存在P2 口鎖存器中。

在S3狀態,P0總線變成高阻懸浮狀態④。在S4狀態,而信號變為有效⑤(是在執行“MOVX A @DFIR'后使而信號有效),而信號使得被尋址的片外PAM略過片刻后把數據送上P0 口總線⑥,當而回到高電平后⑦,P0總線變為懸浮狀態。至此,讀片外RAM周期結束。

寫片外RAM操作時序

向片外RAM寫(存)數據,是8031執行“MOVX @DPTR,A”指令后產生的動作。這條指令執行后,在8031的WR引腳上產生WR信號有效電平,此信號使RAM的WE端被選通。

寫片外RAM的時序如圖7.20(b)所示。開始的過程與讀過程類似,但寫的過程是CPU主動把數據送上P0 口總線,故在時序上,CPU先向P0總線上送完低8位地址后,在S3狀態就將數據送到P0總線③。此間,P0總線上不會出現高阻懸浮現象。

在S4狀態,寫控制信號WR有效,選通片外RAM,稍過片刻,P0上的數據就寫到RAM內了。

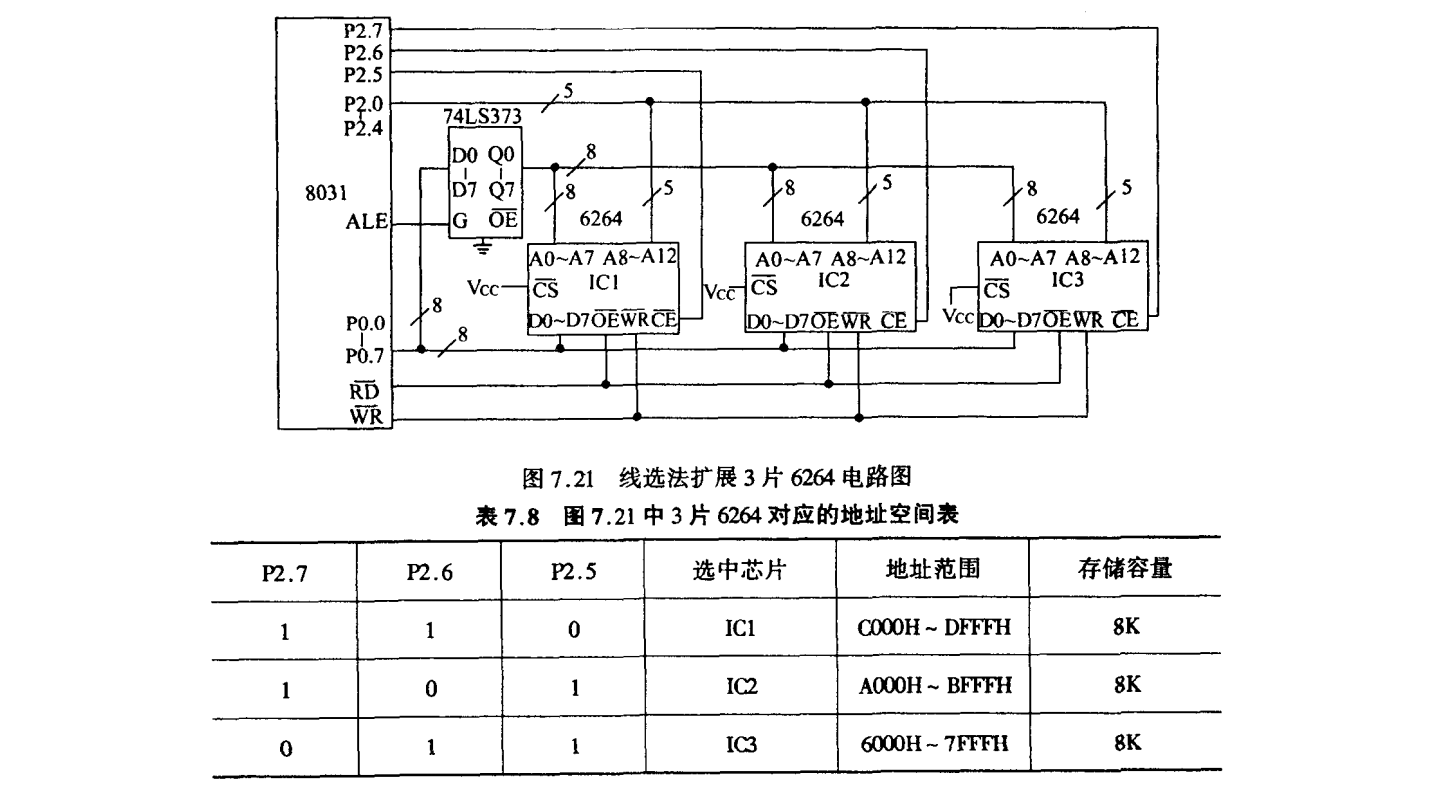

典型的外擴數據存儲器的接口電路

擴展數據存儲器空間地址同外擴程序存儲器一樣,由P2 口提供高8位地址,P0 口分時提供低8位地址和8位雙向數據總線。片外SRAM的讀和寫由8031的RD(P3.7)和WR(P3.6)信號控制,片選端(CE)由地址譯碼器的譯碼輸出控制。因此,SRAM在與單片機連接時,主要解決地址分配、數據線和控制信號線的連接。在與高速單片機連接時,還要根據時序解決速度匹配問題。

圖7.21給出了用線選法擴展8031外部數據存儲器的電路。圖中數據存儲器選用6264,該片地址為A0~A12,故8031剩余地址為三根。用線選法可擴展3片6264。3片6264對應的存儲器空間見表7.8所示。

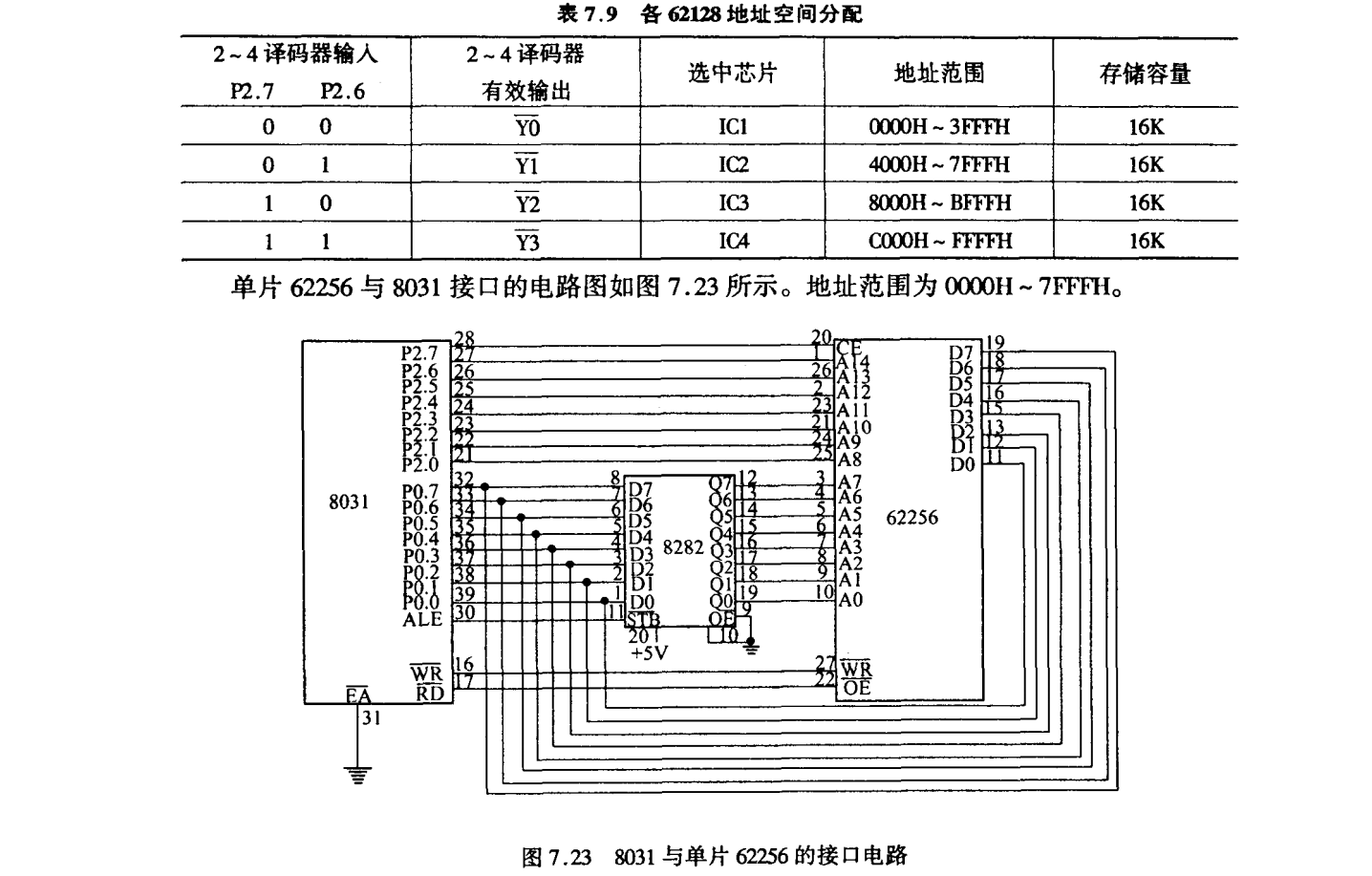

用譯碼選通法擴展8031的外部數據存儲器電路如圖7.22所示。圖中數據存儲器選用62128,該芯片地址線為A0~ A13,這樣8031剩余地址線為兩根,若采用2~4譯碼器可擴展4片62128。各個62128地址分配見表7.9。

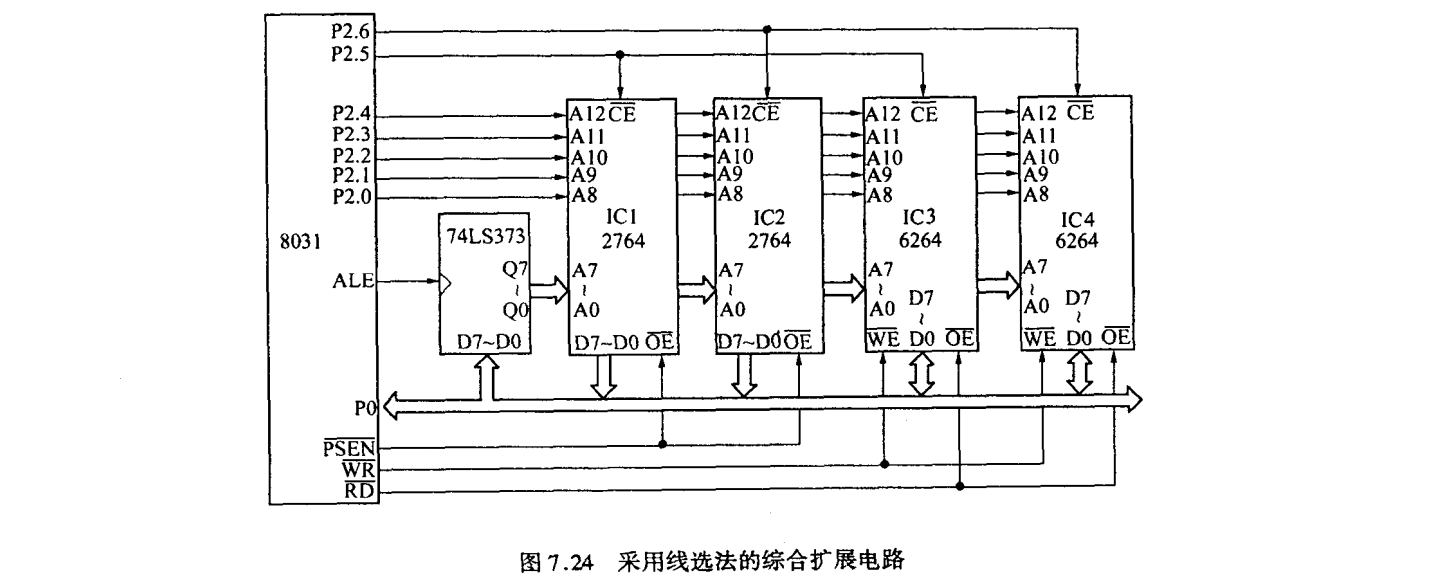

EPROM和RAM的綜合拓展

在單片機應用系統設計中,經常是既要擴展程序存儲器(EPROM)也要擴展數據存儲器(RAM),即存儲器的綜合擴展。下面介紹如何進行綜合擴展。

綜合擴展的硬件接口電路設計

例7.2采用線選法擴展2片8KB的RAM和2片8KB的EPROM。RAM芯片選用2片6264,EPROM芯片選用2片2764,共擴展4片存儲器芯片。擴展接口電路見圖7.24。

控制信號及片選值號

地址線P2.5直接接到IC1(2764)和IC3(6264)的片選反端,P2.6直接接到102(2764)和104(6264)的片選而端。當P2.6 = 0,P2.5 = 1,IC2和IC4型片選端CE低電平,IC1和IC3的CE端全為高電平。

當P2.6=1,P2.5 = 0時IC1和IC3的CE端都是低電平,每次同時選中兩個芯片,具體哪個芯片工作還要通過PSEN、WR、RD控制線控。

當片外程序存儲區讀選通信號PSEN為低電平,肯定到EPROM中讀程序;當讀、寫通信號RD或WR為低電平則到RAM中讀數據或向RAM寫入數據。PSEN、WR、RD三個信號是在執行指令時產生的,但任一時刻,只能執行一條指令,所以只能一個信號有效,其它信號不可能同時有效。

各芯片地址空間分配

硬件電路一旦確定,各芯片的地址范圍實際就已確定,編程時只要給出要選擇芯片的地址,就能准確地選中該芯片。結合圖7.24,介紹IC1、IC2、IC3、IC4地址范圍的確定方法。

程序和數據存儲器地址均用16位,P0 口確定低8位,P2 口確定高8位地址。

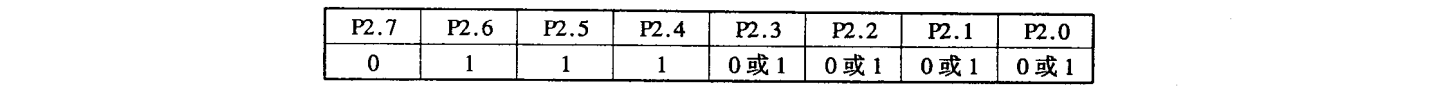

如P2.6 = 0、P2.5=1選中IC2、IC4。地址線A0-A15與P0、P2對應關系如下:

顯然除P2.6、P2.5固定外,其他“ x ”位均可變。設無用位P2.7 = 0,“ x ”各位全為“0”則為最小地址2000H;若“x”位均變為”1“則為最大地址3FFFH,所以IC2和IC4占用地址空間為:2000H-3FFFH 共 8KB。

同理 IC1、IC3 地址范圍 4000H~5FFFH(P2.6= l、P2.5 = 0、P2.7 = 0),IC2與IC4占用相同的地址空間,由於二者一個為程序存儲器,一個為數據存儲器,在控制線PSEN、WR或RD控制下,不同時工作。因此,地址空間重疊也無關系。IC1與IC3也同樣。從此例看出,線選法地址不連續,地址空間利用也不充分,而且地址有重疊。

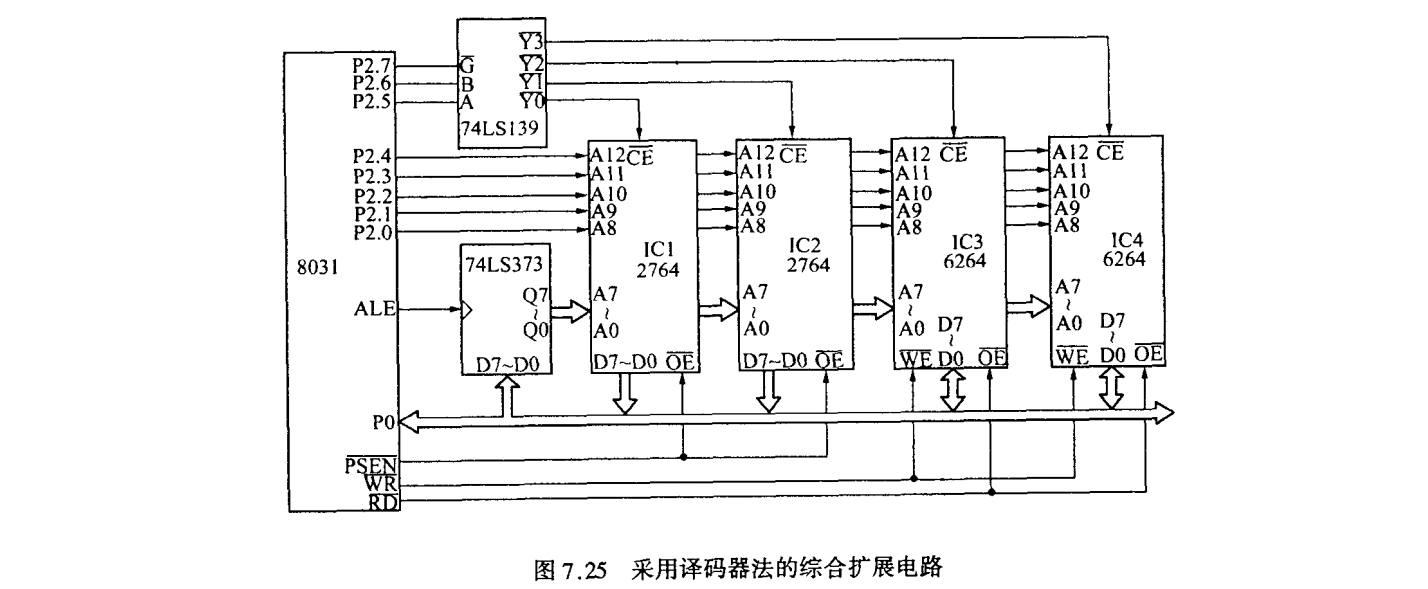

例7.3采用譯碼器法擴展2片8KB EPROM,2片8K BRAM。 EPROM選用2764,RAM選用6264。共擴展4片芯中。擴展的接口電路見圖7.25。圖中74LS139的4個輸出端,Y0 ~ Y3分別連接4個芯片IC1、IC2、IC3、IC4的片選端。Y0~ Y3每次只能有一位是“0”,其他三位全為“1”,輸出為“0”的一端所連接的芯片被選中。

譯碼法地址分配,首先要根據譯碼芯片真值表確定譯碼芯片的輸入狀態,由此再判斷其輸出端選中芯片的地址。

如圖7.25所示74LS139的輸入端A、B、C分別接P2接口的P2.5、P2.6、P2.7三端,召為使能端,低電平有效。根據表7.2中74IS139的真值表可見當C = 0、A = 0、B = 0時,輸出端只有Y0為“0”,Y1~Y3全為1,選中IC1這樣,P2.7、P2.6、P2.5全為“0”其他地址線任意狀態都能選中IClo當其他全為“0”最小地址0000H,其他位全為“1”最大地址為1FFFH。

所以IC1地址范圍0000H~lFFFH。

同理可確定其他芯片地址范圍如下:

IC2:2000H~3FFFH

IC3:4000H-5FFFH

IC4:6000H~7FFFH

顯然地址空間是連續的。