本文同時發表在https://github.com/zhangyachen/zhangyachen.github.io/issues/132

最近在研究計算機里的基本邏輯電路,想到一個問題:為什么CPU需要時鍾這樣的概念?

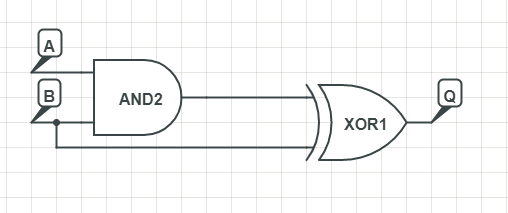

首先考慮如下邏輯電路:

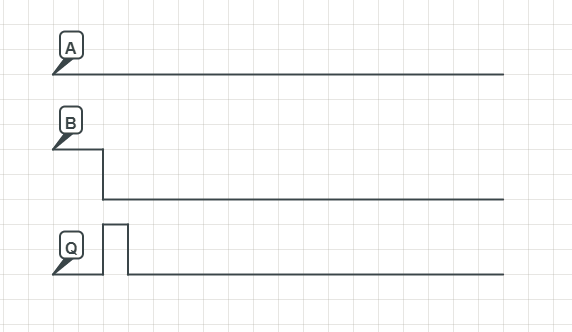

當A=B=1時,Q=0。當輸入信號發生變化時,邏輯元件不會立即對輸入變化做出反應,會有一個傳播時延(propagation delay)。當B變化為0時,由於B也作為XOR的直接輸入,所以XOR異或門會立即感知一個輸入變為0的狀態變化,XOR輸出變為了1。但是由於傳播時延的作用,AND與門的輸出會過一小段時間才變為0,XOR的輸出會在變為1后隔一小段時間重現變為0。表現為下圖就是這樣:

上面這種現象叫作空翻(race condition),即指輸出中出現了一個不希望有的脈沖信號。

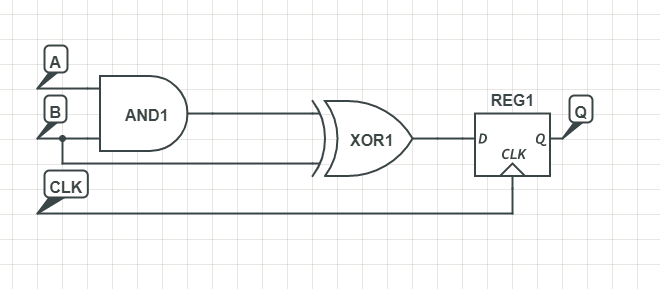

一個簡單的辦法就是在輸出端放置一個邊沿觸發器:

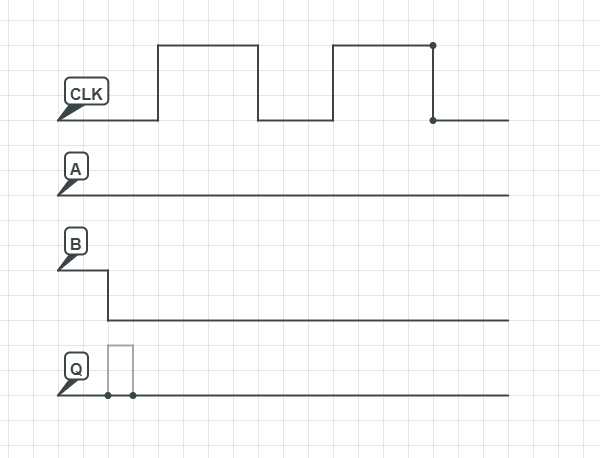

邊沿觸發器的作用就是只有當CLK端輸入從0變到1時,數據端D的輸入才會影響邊沿觸發器的輸出。這樣,所有的傳播時延都會被邊沿觸發器所隱藏掉,這時Q端的輸出將變得穩定。比如:

其中灰色的部分代表沒有邊沿觸發器時的Q端輸出狀態。我們可以看出,當有了邊沿觸發器后,Q端的輸出變得穩定,基本消除了傳播時延。

從上面的例子我們可以看出CPU為什么要時鍾:目前絕大多數的微處理器都是被同步時序電路所驅動,而時序電路由各種邏輯門組成。正如上面說的那樣,邏輯門需要一小段時間對輸入的變化做出反應(propagation delay)。所以需要時鍾周期來容納傳播時延,並且時鍾周期應當大到需要容納所有邏輯門的傳播時延。

當然,目前也有Asynchronous sequential logic,即不需要時鍾信號做同步。但是這種異步邏輯電路雖然速度比同步時序電路快,然而設計起來比同步時序電路復雜的多,並且會遇到上面說的空翻現象(race condition),所以,現在絕大多數的CPU還是需要時鍾做信號同步的。

參考資料: